Brother International HL-720 Service Manual - Page 28

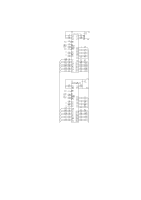

CPU Receiving Mode, This supports the IEEE1284 data transfer with the following mode.

|

View all Brother International HL-720 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 28 highlights

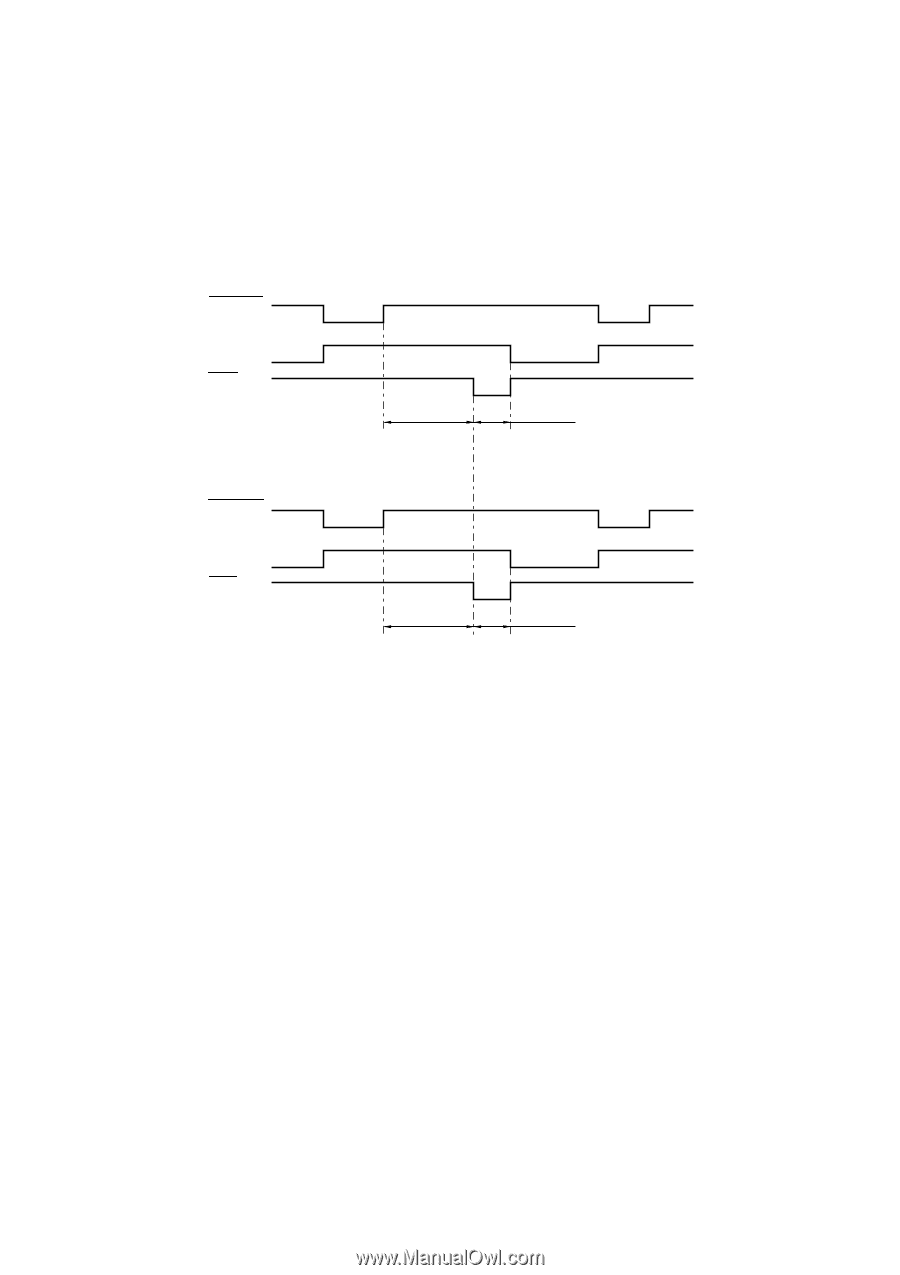

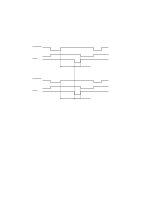

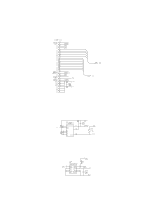

(7) CDCC parallel I/O There are two modes in this unit. One is the CPU receiving mode and the other is the DMA receiving mode. In the CPU receiving mode the CPU receives the command data from the PC, and after the CPU is switched to the DMA mode, it receives the image data and writes to the DRAM directly. CPU Receiving Mode STROBE BUSY ACK 90 µsec 0.5 µsec STROBE BUSY ACK 1.5 µsec 0.5 µsec BUSY goes HIGH at the falling edge of STROBE. The data (8 bits) from the PC is latched in the data buffer at the rising edge of STROBE. The pulse width of ACK differs according to the speed MODE as shown above. BUSY goes LOW at the rising edge of ACK. This supports the IEEE1284 data transfer with the following mode. Nibble mode Byte mode (8) Data extension This circuit extents the compressed image data which are received from the PC, and writes the bit map data to the FIFO. (9) Software support Supports 16 x 16 rotation, bit expansion, and bit search. (10)EEPROM I/O One output port and one I/O port are assigned. II-11