HP BL25/35/45p HP ProLiant Network Adapter Software and Configuration Guide - Page 36

B11. RBUF Cluster list, B9. RBUF via GRC

|

View all HP BL25/35/45p manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 36 highlights

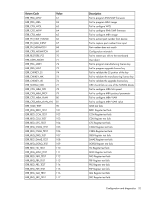

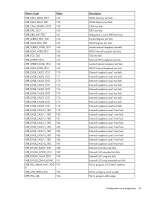

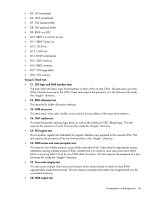

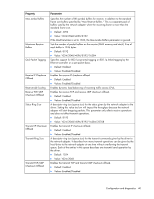

• B5. CP scratchpad • B6. MCP scratchpad • B7. TAS header buffer • B8. TAS payload buffer • B9. RBUF via GRC • B10. RBUF via indirect access • B11. RBUF Cluster list • B12. TSCH list • B13. CSCH List • B14. RV2P scratchpads • B15. TBDC memory • B16. RBDC memory • B17. CTX page table • B18. CTX memory Group C: Block tests • C1. CPU logic and DMA interface tests The tests check the basic logic functionalities of each of the on-chip CPUs. The tests also cover the DMA interface exposed to the CPUs. These tests require the presence of a test firmware file inside the "diagfw" directory. • C2. RBUF allocation test This tests the Rx buffer allocation interface. • C3. CAM access test This tests read, write, add, modify, and cache hit functionalities of the associative memory. • C4. TPAT cracker test This tests the packet cracking logic block as well as the checksum/CRC offload logic. This test requires the presence of a test firmware file inside the "diagfw" directory. • C5. FIO register test This is another register test dedicated for register interface only exposed to the internal CPUs. This test requires the presence of the test firmware files in the "diagfw" directory. • C6. NVM access and reset-corruption tests This tests the non-volatile memory access (both read and write). It also tests for appropriate access arbitration among multiple entities (CPUs). Another test is to check to issue chip reset while NVM block is servicing data to look for any NVM data corruption. This test requires the presence of a test firmware file inside the "diagfw" directory. • C7. Core-reset integrity test This test issues multiple chip resets and constant driver load/unload to check for boot ROM appropriately loads the bootcode. This test requires a proper bootcode to be programmed into the non-volatile memory. • C8. DMA engine test Configuration and diagnostics 36