Canon PowerShot 350 Service Manual - Page 34

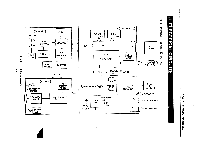

Camera, Block, Diagram

|

View all Canon PowerShot 350 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

Part 2: Technical Information 1.2 CAMERA BLOCK DIAGRAM Lens unit C -Flash Block IRIS-A IRIS-B Camera CBA CCD (1/3" VGA) CCD OUT 4) R (pH H-Driver .4 H, V-Driver V, SUB, CH1 ST1 Light metering Light metering Sensor Circuit Flash Flash Charge Circuit STR-TRG STO ST1 CDS, AGS II.O AD IN A DS1, DS2, CPOB, PBLK, CP2 A 1 I CG A HD VD3 CGDATA CGSCK EXFCK 2FCK BUFFER OSC 0 24.54 MHz I-I EVR AGC, PEDE, AD APA, OB, KNEE RBIAS, V-SUB, LC O REC(L) O IRIS-A IRIS-B EVR 0 (SERIAL) >co >0 a2C., «02 > 0 0 2 >co 2 0 a >c9 a 2 0 o z 0 Fig. 2-2 Camera Block The "Camera" block (section) includes the lens aperture diaphragm and its IRIS drive and control circuits. the CCD, CCD Driver, the analog video processor which processes the CCD OUT signal. It also has the system clock generating oscillator (OSC) which is used to develop all the clock pulses in CG. The automatic flash system is also a part of the "Camera" block. The IRIS control within the lens unit is controlled by two signals, IRIS-A and ISIS-B to provide two aperture settings, f/8 (actually f/7 + ND25) and f/2.8 respectively. 2-2