Canon PowerShot 350 Service Manual - Page 37

processing

|

View all Canon PowerShot 350 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

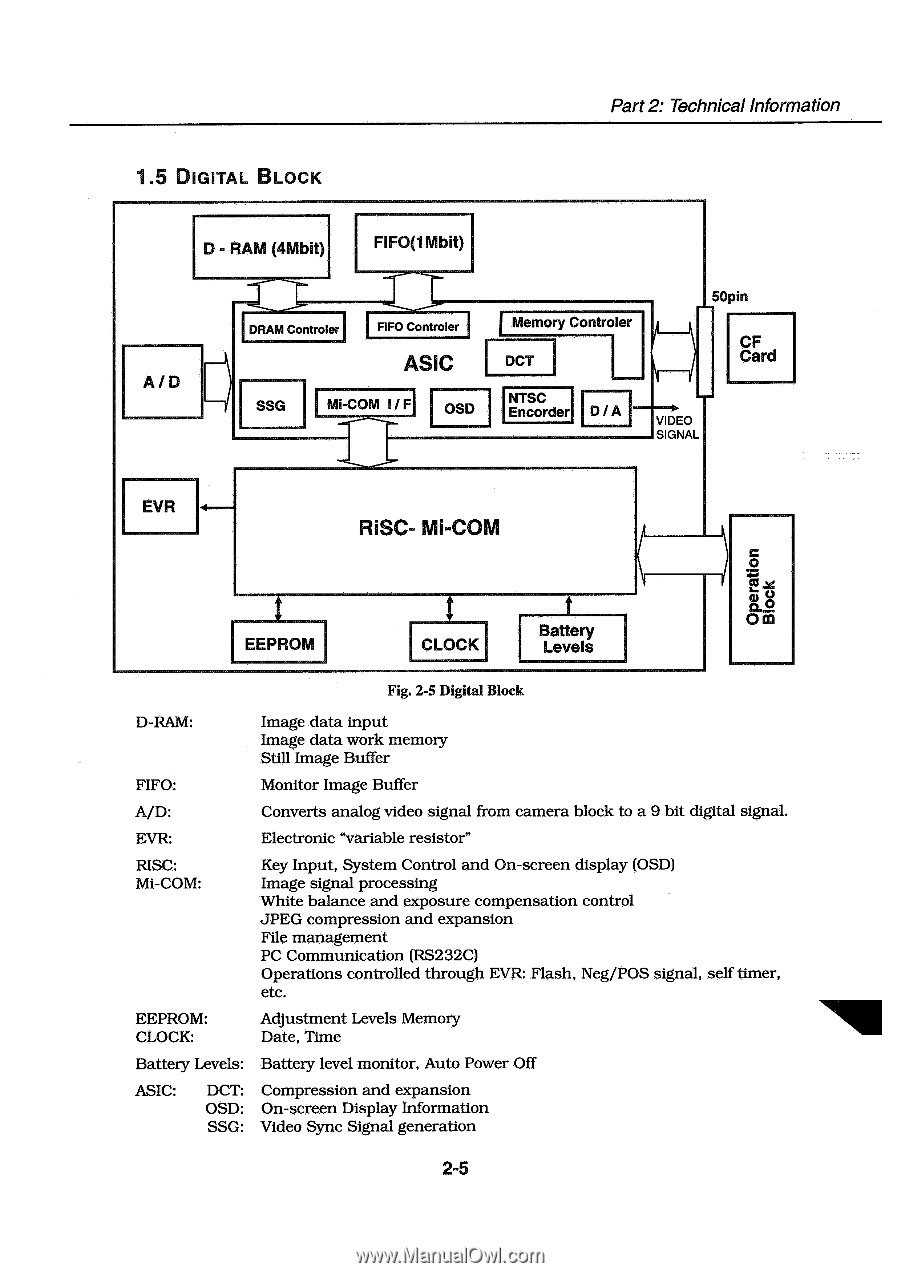

Part 2: Technical Information 1.5 DIGITAL BLOCK D- RAM (4Mbit) FIF0(1Mbit) A/D DRAM Controler FIFO Controler ASIC I SSG Mi-COM I / F OSD Memory Controler DCT 50pin CF Card NTSC Encorder D/A VIDEO SIGNAL EVR RISC- Mi-COM EEPROM CLOCK Battery Levels Fig. 2-5 Digital Block D-RAM: Image data input Image data work memory Still Image Buffer FIFO: Monitor Image Buffer A/D: Converts analog video signal from camera block to a 9 bit digital signal. EVR: Electronic "variable resistor" RISC: Mi-COM: Key Input, System Control and On-screen display (OSD) Image signal processing White balance and exposure compensation control JPEG compression and expansion File management PC Communication (RS232C) Operations controlled through EVR: Flash, Neg/POS signal, self timer, etc. EEPROM: CLOCK: Adjustment Levels Memory Date, Time Battery Levels: Battery level monitor, Auto Power Off ASIC: DCT: Compression and expansion OSD: On-screen Display Information SSG: Video Sync Signal generation 2-5