Dell PowerEdge R760XA Installation and Service Manual - Page 41

Table 37. Processor Settings details continued, Table 38. Processor n details, CPU Crash Log Support

|

View all Dell PowerEdge R760XA manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 41 highlights

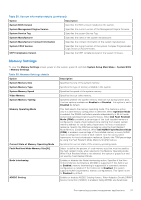

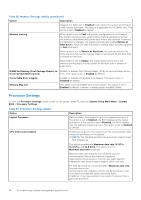

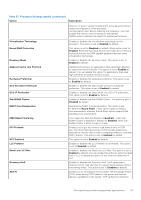

Table 37. Processor Settings details (continued) Option Processor Core Speed Processor Bus Speed Description uncore power budgeting. This option is set to Enabled by default. Specifies the maximum core frequency of the processor. Specifies the bus speed of the processor. NOTE: The processor bus speed option displays only when both processors are installed. Local Machine Check Exception CPU Crash Log Support UPI3 Link Control Enables or disables the local machine check exception. This is an extension of the MCA Recovery mechanism providing the capability to deliver Uncorrected Recoverable (UCR) Software Recoverable Action Required (SRAR) errors to one or more specific logical processors threads receiving previously poisoned or corrupted data. When enabled, the UCR SRAR Machine Check Exception is delivered only to the affected thread rather than broadcast to all threads in the system. The feature supports operating system recovery for cases of multiple recoverable faults that are detected close, which would otherwise result in a fatal machine check event. The feature is available only on Advanced RAS processors. This option is set to Enabled by default. This field controls Intel CPU Crash Log feature for collection of previous crash data from shared SRAM of Out-of-Band Management Services Module at post reset. This option is set to Disabled by default. Set the value of UPI3 which is the QPI Link Control for the CPU's. This field is provided due to CPU issue of crosstalk from UPI Port3 affecting lane 0 Rx margins of PCIe Port3 (PE3) when operating at Gen5 Speed. Disabled - Disables UPI3 link and allow the PE3 port A to reach Gen 5 speed (32GT/s). Enabled - Enables UPI3 link and limit the PE3 port A to Gen4 speed (16GT/s). NOTE: This option is dynamically shown or hidden due to CPU constraint. Processor n NOTE: Depending on the number of processors, there might be up to n processors listed. The following settings are displayed for each processor: Table 38. Processor n details Option Family-Model-Stepping Brand Level 2 Cache Level 3 Cache Number of Cores Microcode Description Specifies the family, model, and stepping of the processor as defined by Intel. Specifies the brand name. Specifies the total L2 cache. Specifies the total L3 cache. Specifies the number of cores per processor. Specifies the processor microcode version. Pre-operating system management applications 41