HP rp8420 HP 9000 rp8420 Server - User Service Guide, Fifth Edition - Page 31

System Backplane to PCI-X Backplane Connectivity, Clocks and Reset, I/O Subsystem

|

View all HP rp8420 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 31 highlights

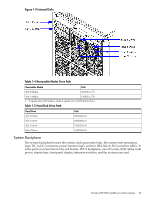

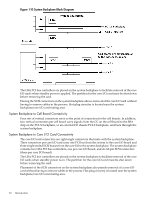

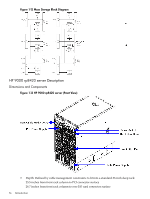

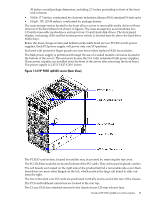

System Backplane to PCI-X Backplane Connectivity The PCI-X backplane uses two connectors for the SBA link bus and two connectors for the high-speed data signals and the manageability signals. SBA link bus signals are routed through the system backplane to the CC on each corresponding cell board. The high-speed data signals are routed from the SBA chips on the PCI-X backplane to the two LBA PCI bus controllers on the system backplane. Clocks and Reset The system backplane contains reset and clock circuitry that propagates through the whole system. The system backplane central clocks drive all major chip set clocks. I/O Subsystem The cell board to the PCI-X board path runs from the CC to the SBA, from the SBA to the ropes, from the ropes to the LBA, and from the LBA to the PCI slots seen in Figure 1-11. The CC on cell board 0 and cell board 1 communicates through an SBA over the SBA link. The SBA link consists of both an inbound and an outbound link with an effective bandwidth of approximately 1 GB/sec. The SBA converts the SBA link protocol into "ropes." A rope is defined as a high-speed, point-to-point data bus. The SBA can support up to 16 of these high-speed, bi-directional rope links for a total aggregate bandwidth of approximately 4 GB/sec. Each LBA acts as a bus bridge, supporting either one or two ropes and capable of driving 33 MHz or 66 MHz for PCI cards. The LBAs can also drive at 66 MHz or 133 MHz for PCI-X cards. When cell board 2 and cell board 3 are present, the cell boards attach to their own associated SBA and LBA chips on the PCI-X board in the Server Expansion Unit. Detailed HP 9000 rp8420 server Description 31