Cisco ASR1006 Hardware Installation Guide - Page 115

Codec Complexity or Service, Maximum Supported Density per - asr x chassis

|

UPC - 882658196423

View all Cisco ASR1006 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 115 highlights

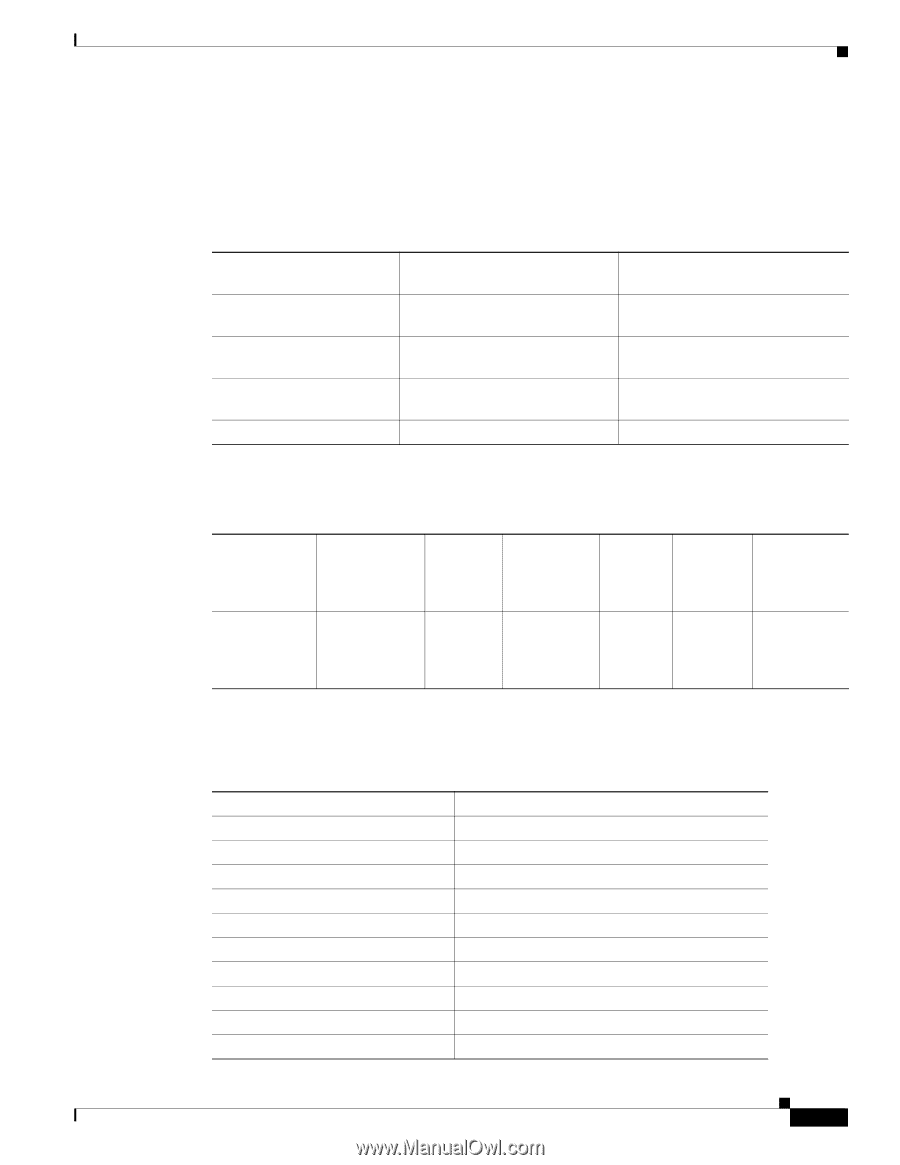

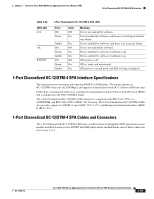

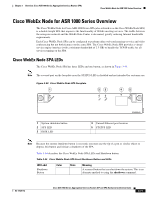

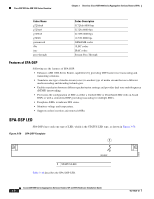

Chapter 3 Overview: Cisco ASR 1000 Series Aggregation Services Routers SPAs Cisco DSP SPA for ASR 1000 Series Overview OL-14126-12 Each SPA-DSP comprises of seven SP2603 DSP chips having a total of 21 DSP cores (three DSP cores per SP2603). Based on the complexity of codec (low, medium, high), the density or maximum number of channels supported per DSP core and maximum channels supported per SPA-DSP are defined. Table 3-45 provides a matrix for the maximum number of channels supported on the DSP core and on SPA-DSP, and the complexity type: Table 3-45 Codec Complexity and Density Supported Matrix Maximum Supported Density per Codec Complexity or Service DSP Core LC (Low complexity) 43 Voice/xcode MC (Medium complexity) 28 Voice/xcode HC (High Complexity) 17 Voice/xcode ISAC Voice/xcode 8 Maximum Supported Density per SPA-DSP 903 588 357 168 Table 3-46 provides hardware and software compatibility details for a SPA-DSP. Table 3-46 SPA-DSP Hardware and Software Compatibility Type of DSP SPA (Product ID) SPA-DSP ASR1000 Router Route Chassis Processor Supported Supported ASR 1002, ASR 1004, and ASR 1006 Chassis RP1 and RP2 Power SIPs ESPs Requirements Supported Supported 25 watts SIP-10 and SIP-40 ESP-10 and ESP-40 Minimum Cisco IOS XE Release Supported Cisco IOS XE Release 3.2S The SPA-DSP supports transcoding for the codecs listed in Table 3-47. Table 3-47 SPA-DSP-Supported Transcoding Codec List Codec Name g711alaw g711ulaw g722-64 g723r53 g723r63 g726r16 g726r24 g726r32 g726r40 g728 Codec Description G.711 A Law 64000 bps G.711 u Law 64000 bps G722r64 G.723.1 5300 bps G.723.1 6300 bps G.726 16000 bps G.726 24000 bps G.726 32000 bps G.726 40000 bps G.728 codec Cisco ASR 1000 Series Aggregation Services Routers SIP and SPA Hardware Installation Guide 3-73