HP Visualize b180L hp Visualize workstation b132L, b132L plus, b160L, b180L se - Page 105

HPMC Caused by a Multi-Bit Memory, Parity Error

|

View all HP Visualize b180L manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 105 highlights

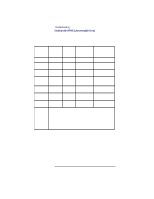

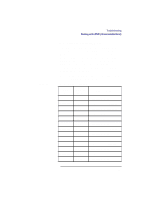

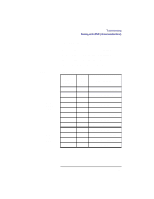

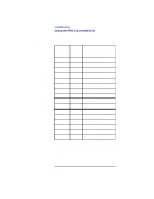

Table 9 Troubleshooting Dealing with HPMC (Uncorrectable Error) HPMC Caused by a Multi-Bit Memory Parity Error An HPMC interruption is forced when a multi-bit memory parity error is detected during a "DMA read" operation of fetching an I/D cache line (32 bytes). Table 9 shows an example of the HPMC error information retrieved from Stable Storage by the PIM_INFO command during the Boot Administration environment. Multi-Bit Memory Parity Error Word Value Check Type CPU State Cache Check TLB check Bus Check Assists Check Assists State System Responder Address System Requester Address System Controller Status 0x20000000 0x9e000004 0x00000000 0x00000000 0x00210004 0x00000000 0x00000000 0x00nnnnnn 0x00000000 0x00000nnn 83

Troubleshooting

Dealing with HPMC (Uncorrectable Error)

83

HPMC Caused by a Multi-Bit Memory

Parity Error

An HPMC interruption is forced when a multi-bit

memory parity error is detected during a “DMA read”

operation of fetching an I/D cache line (32 bytes).

Table 9 shows an example of the HPMC error infor-

mation retrieved from Stable Storage by the

PIM_INFO command during the Boot Administration

environment.

Table 9

Multi-Bit Memory Parity Error

Word

Value

Check Type

0x20000000

CPU State

0x9e000004

Cache Check

0x00000000

TLB check

0x00000000

Bus Check

0x00210004

Assists Check

0x00000000

Assists State

0x00000000

System Responder Address

0x00nnnnnn

System Requester Address

0x00000000

System Controller Status

0x00000nnn