Dell Broadcom NetXtreme Family of Adapters Broadcom NetXtreme II Network Adapt - Page 192

Group D: Ethernet Traffic Tests

|

View all Dell Broadcom NetXtreme Family of Adapters manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 192 highlights

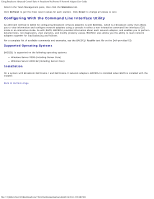

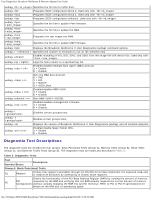

User Diagnostics: Broadcom NetXtreme II Network Adapter User Guide NVM Access Verifies non-volatile memory (NVM) accesses (both read and write) initiated by one of the internal C6 and Reset- CPUs. It tests for appropriate access arbitration among multiple entities (CPUs). It also checks for Corruption possible NVM corruption by issuing a chip reset while the NVM block is servicing data. C7 Core-Reset Verifies that the chip performs its reset operation correctly by resetting the chip multiple times, Integrity checking that the bootcode and the internal uxdiag driver loads/unloads correctly. Verifies the functionality of the DMA engine block by performing numerous DMA read and write operations to various system and internal memory locations (and byte boundaries) with varying C8 DMA Engine lengths (from 1 byte to over 4 KB, crossing the physical page boundary) and different data patterns (incremental, fixed, and random). CRC checks are performed to ensure data integrity. The DMA write test also verifies that DMA writes do not corrupt the neighboring host memory. C9 VPD Exercises the Vital Product Data (VPD) interface using PCI configuration cycles and requires a proper bootcode to be programmed into the non-volatile memory. If no VPD data is present (i.e., the VPD NVM area is all 0s), the test first initializes the VPD data area with non-zero data before starting the test and restores the original data after the test completes. C11 FIO Events Verifies that the event bits in the CPU's Fast IO (FIO) interface are triggering correctly when a particular chip events occur, such as a VPD request initiated by the host, an expansion ROM request initiated by the host, a timer event generated internally, toggling any GPIO bits, or accessing NVM. Group D: Ethernet Traffic Tests Enables MAC loopback mode in the adapter and transmits 5000 Layer 2 packets of various sizes. As D1 MAC Loopback the packets are received back by Broadcom NetXtreme II User Diagnostics, they are checked for errors. Packets are returned through the MAC receive path and never reach the PHY. The adapter should not be connected to a network. Enables PHY loopback mode in the adapter and transmits 5000 Layer 2 packets of various sizes. As D2 PHY Loopback the packets are received back by Broadcom NetXtreme II User Diagnostics, they are checked for errors. Packets are returned through the PHY receive path and never reach the wire. The adapter should not be connected to a network. D4 LSO Verifies the functionality of the adapter's Large Send Offload (LSO) support by enabling MAC loopback mode and transmitting large TCP packets. As the packets are received back by Broadcom NetXtreme II User Diagnostics, they are checked for proper segmentation (according to the selected MSS size) and any other errors. The adapter should not be connected to a network. D5 EMAC Statistics Verifies that the basic statistics information maintained by the chip is correct by enabling MAC loopback mode and sending Layer 2 packets of various sizes. The adapter should not be connected to a network. D6 RPC Verifies the Receive Path Catch-up (RPC) block by sending packets to different transmit chains. The packets traverse the RPC logic (though not the entire MAC block) and return to the receive buffers as received packets. This is another loopback path that is used by Layer 4 and Layer 5 traffic within the MAC block. As packets are received back by Broadcom NetXtreme II User Diagnostics, they are checked for errors. The adapter should not be connected to a network. Please read all Restrictions and Disclaimers. Back to Contents Page file:///T|/htdocs/NETWORK/BroadCom/71921/NetXtremeII/en/userdiag.htm[9/26/2012 3:29:54 PM]