Intel BX80601920 Data Sheet - Page 20

Platform Environmental Control Interface PECI, DC Specifications

|

UPC - 735858204736

View all Intel BX80601920 manuals

Add to My Manuals

Save this manual to your list of manuals |

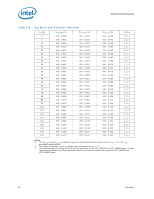

Page 20 highlights

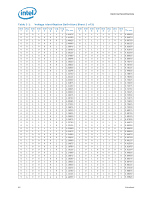

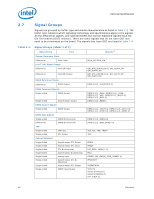

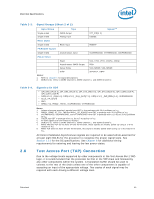

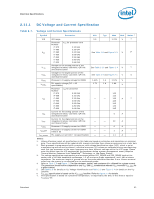

Electrical Specifications 2.9 Platform Environmental Control Interface (PECI) DC Specifications PECI is an Intel proprietary interface that provides a communication channel between Intel processors and chipset components to external thermal monitoring devices. The processor contains a Digital Thermal Sensor (DTS) that reports a relative die temperature as an offset from Thermal Control Circuit (TCC) activation temperature. Temperature sensors located throughout the die are implemented as analog-to-digital converters calibrated at the factory. PECI provides an interface for external devices to read the DTS temperature for thermal management and fan speed control. More detailed information may be found in the Platform Environment Control Interface (PECI) Specification. 2.9.1 Table 2-5. DC Characteristics The PECI interface operates at a nominal voltage set by VTTD. The set of DC electrical specifications shown in Table 2-5 is used with devices normally operating from a VTTD interface supply. VTTD nominal levels will vary between processor families. All PECI devices will operate at the VTTD level determined by the processor installed in the system. For specific nominal VTTD levels, refer to Table 2-7. PECI DC Electrical Limits Symbol Vin Vhysteresis Vn Vp Isource Isink Ileak+ IleakCbus Vnoise Definition and Conditions Input Voltage Range Hysteresis Negative-edge threshold voltage Positive-edge threshold voltage High level output source (VOH = 0.75 * VTTD) Low level output sink (VOL = 0.25 * VTTD) High impedance state leakage to VTTD (Vleak = VOL) High impedance leakage to GND (Vleak = VOH) Bus capacitance per node Signal noise immunity above 300 MHz Min -0.150 0.1 * VTTD 0.275 * VTTD 0.550 * VTTD -6.0 Max VTTD N/A 0.500 * VTTD 0.725 * VTTD N/A Units V V V V Notes1 mA 0.5 1.0 mA N/A 100 µA 2 N/A N/A 0.1 * VTTD 100 10 N/A µA 2 pF Vp-p Notes: 1. VTTD supplies the PECI interface. PECI behavior does not affect VTTD min/max specifications. 2. The leakage specification applies to powered devices on the PECI bus. 20 Datasheet