Intel BX80601920 Data Sheet - Page 86

Sleep States, ACPI P-States Intel, Turbo Boost Technology

|

UPC - 735858204736

View all Intel BX80601920 manuals

Add to My Manuals

Save this manual to your list of manuals |

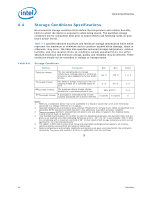

Page 86 highlights

Features 7.2.2.4 If Intel QPI L1 has been granted, the processor will disable some clocks and PLLs and for processors with an integrated memory controller, the DRAM will be put into selfrefresh. Package C6 State The package will enter the C6 low power state when all cores are in the C6 or lower power state and the processor has been granted permission by the other component(s) in the system to enter the C6 state. The package will also enter the C6 state when all cores are in an idle state lower than C6 but the other component(s) have only granted permission to enter C6. If Intel QPI L1 has been granted, the processor will disable some clocks and PLLs and the shared cache will enter a deep sleep state. Additionally, for processors with an integrated memory controller, the DRAM will be put into self-refresh. 7.3 Sleep States The processor supports the ACPI sleep states S0, S1, S3, and S4/S5 as shown in Table 7-3. For information on ACPI S-states and related terminology, refer to ACPI Specification. The S-state transitions are coordinated by the processor in response PM Request (PMReq) messages from the chipset. The processor itself will never request a particular S-state. Table 7-3. Processor S-States S-State Power Reduction S0 S1 S3 S4/S5 Normal Code Execution Cores in C1E like state, processor responds with CmpD(S1) message. Memory put into self-refresh, processor responds with CmpD(S3) message. Processor responds with CmpD(S4/S5) message. Allowed Transitions S1 (using PMReq) S0 (using reset or PMReq) S3, S4 (using PMReq) S0 (using reset) S0 (using reset) Notes: 1. If the chipset requests an S-state transition, which is not allowed, a machine check error will be generated by the processor. 7.4 ACPI P-States (Intel® Turbo Boost Technology) The processor supports ACPI P-States. A new feature is that the P0 ACPI state will be a request for Intel Turbo Boost Technology. This technology opportunistically and automatically allows the processor to run faster than its marked frequency if the processor is operating below power, thermal, and current specifications. Maximum turbo frequency is dependant on the processor component and number of active cores. No special hardware support is necessary for Intel Turbo Boost Technology. BIOS and the operating system can enable or disable Intel Turbo Boost Technology. 86 Datasheet