ZyXEL Elite 2864 User Guide - Page 98

S25=0, S41b2, S41b0, S38b5

|

View all ZyXEL Elite 2864 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 98 highlights

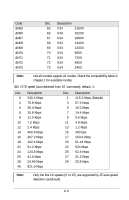

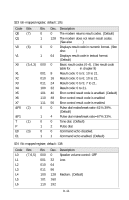

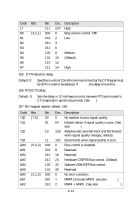

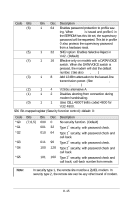

Code Bits Bin. L7 111 N0 (3,2,1) 000 N1 001 N2 010 N3 011 N4 100 N5 101 N6 110 N7 111 Dec. Description 224 High. 0 Ring volume control: OFF 2 Low. 4 6 8 Medium. 10 (Default) 12 14 High. S25 DTR detection delay; Default: 0: Specifies in units of 10ms the minimum time that the DTR signal must be OFF in order to be detected. If S25=0, the delay time is 4ms. S26 RTS/CTS delay; Default: 0: Sets the delay, in 10 millisecond units, between RTS and modem's CTS response in synchronous mode. (See &Rn) S27 Bit-mapped register; default: 156: Code Bits Bin. *Q0 (7,6) 00 *Q1 01 *Q2 10 *Q3 11 &H0 (5,4,3) 000 &H1 001 &H2 010 &H3 011 &H4 100 &H5 101 &K0 (2,1,0) 000 &K1 001 &K2 010 Dec. Description 0 No reaction to poor signal quality. 64 Initiates retrain if signal quality is poor. (See also S41b2) 128 Adaptive rate (auto fall-back and fall-forward when signal quality changes; default) 192 Disconnects when signal quality is poor. 0 Flow control is disabled. 8 Reserved. 16 Reserved. 24 Hardware CTS/RTS flow control. (Default) 32 Software XON/XOFF flow control. 40 Reserved. 0 No error correction. 1 MNP4 (Includes MNP3, see also S41b0). 2 MNP4 + MNP5. (See also S41b0, S38b5) 8-12