Intel X38ML Product Specification - Page 106

Examples of Event Data Field Contents for Memory Errors, 2.3.3, PCI Error Events

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

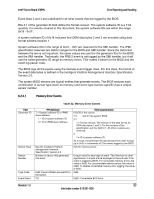

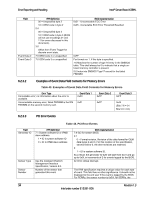

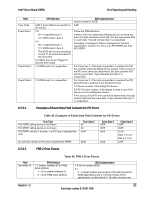

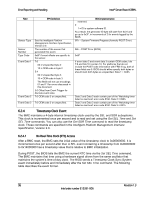

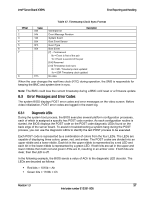

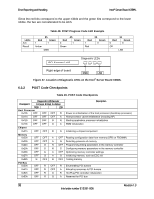

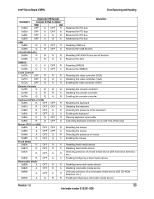

Page 106 highlights

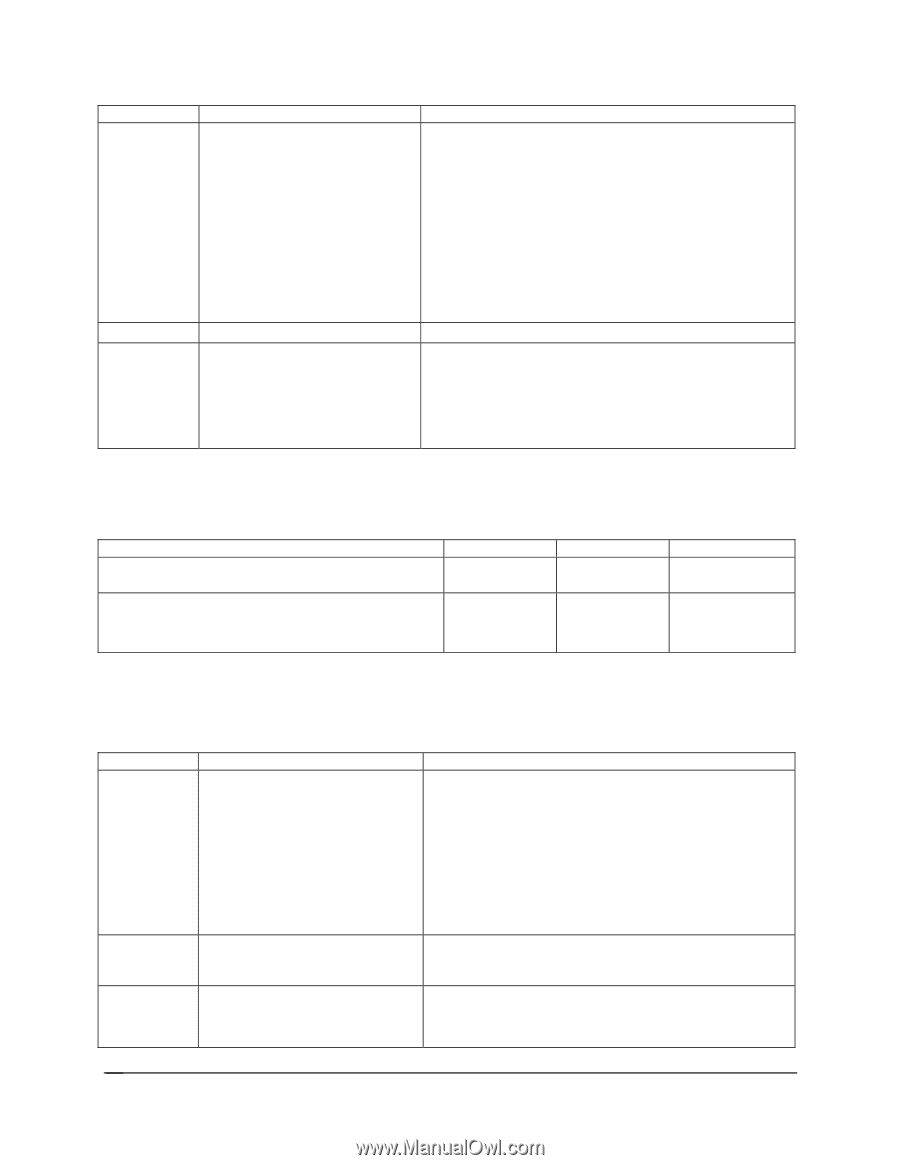

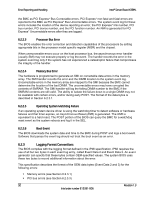

Error Reporting and Handling Intel® Server Board X38ML Field Event Data 2 Event Data 3 IPMI Definition 00 = Unspecified byte 2 10 = OEM code in byte 2 5:4 00 = Unspecified byte 3 10 = OEM code in byte 3 (BIOS will not use encodings 01 and 11 for errors discussed in this document). 3:0 Offset from Event Trigger for discrete event state. 7:0 OEM code 2 or unspecified 7:0 OEM code 3 or unspecified BIOS Implementation 0x21 - Uncorrectable ECC Error 0x25 - Correctable ECC Error Threshold Reached 0xFF For format rev 1, if this byte is specified. 7:6 Matches the number of type 16 entry in the SMBIOS table. This shall always be 0 to indicate that a single onboard memory controller is present. 5:0 Index into SMBIOS Type17 record for the failed FBDIMM. 6.2.3.2 Examples of Event Data Field Contents for Memory Errors Table 43. Examples of Event Data Field Contents for Memory Errors Error Type Correctable error; no information about the error is available. Uncorrectable memory error, failed FBDIMM is the fifth FBDIMM on the second memory card. Event Data 1 0x20 0x21 Event Data 2 0xFF 0xFF Event Data 3 0xFF 0x44 (Bits 7:6 = 01 Bits 5:0 = 04) 6.2.3.3 PCI Error Events Table 44. PCI Error Events Field Generator ID IPMI Definition 7:1 System software ID or IPMB slave address. 1 = ID is system software ID 0 = ID is IPMB slave address Sensor Type Sensor Number See the Intelligent Platform Management Interface Specification, Version 2.0. Number of the sensor that generated this event BIOS Implementation 7:4 0x3 for system BIOS. 3:1 0 = Format revision, Revision of the data format for OEM data bytes 2 and 3. For this revision of the specification, set this field to 0. All other revisions are reserved. 0 1 = ID is system software ID. As a result, the generator ID byte will start from 0x31 and go up to 0x3f, in increments of 2 for events logged by the BIOS. 0x13 for critical interrupt. The IPMI specification requires a unique value for each type of event. This field has no other significance. It should not be displayed to the end user if the event is logged by the BIOS. For PERRs, the sensor number is 0xEA, for SERRs, the 94 Revision 1.3 Intel order number E15331-006