Intel X38ML Product Specification - Page 68

Power-up Sequence, Power Down Sequence, Power Control Sources

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 68 highlights

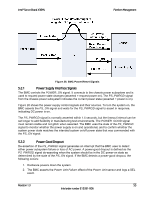

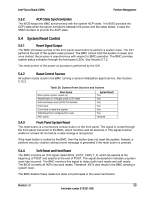

Platform Management Intel® Server Board X38ML 3. The BMC waits 10 seconds. If the power state retention feature is configured to power on the server after an AC loss, it attempts to power up the server. This is the case when either the AC dropped out momentarily, but not long enough to reset the BMC, or the power subsystem had a momentary failure that the BMC could not differentiate from a momentary AC loss. The BMC responds to the power loss interrupt with 1 to 2 ms if it is in operational mode. 5.2.3 Power-up Sequence To power up the server, the BMC simulates the front panel power button being pressed for 8 seconds or until PS_PWRGD is asserted. If PS_PWRGD is not asserted within 8 seconds, then a fault is generated. See Section 5.17.3. After simulating the front panel power button press, the BMC initializes all sensors to their power-on initialization state. The initialization agent is run. 5.2.4 Power Down Sequence To power down the system, the BMC simulates the front panel power button being pressed for 8 seconds or until PS_PWRGD is deasserted. If PS_PWRGD is not deasserted within 8 seconds, then a fault is generated. See Section 5.17.3. Before initiating the system power down, the BMC stops scanning any sensors that should not be scanned in the powered-down state. 5.2.5 Power Control Sources The following sources can initiate power-up and/or power-down activity: Source Power button BMC watchdog timer Platform event filtering Command Power state retention Chipset Table 27. Power Control Initiators External Signal Name or Internal Subsystem Front panel power button Internal BMC timer PEF Routed through command processor Implemented via BMC internal logic Sleep S4/S5 signal (same as POWER_ON) Capabilities Turns power on or off Turns power off, or power cycle Turns power off, power cycle, or reset Turns power on or off, or power cycle Turns power on when AC power returns Turns power on or off 5.2.5.1 Power Button Signal The POWER_BUTTON signal toggles the system power. This signal is activated by a momentary contact switch on the front panel assembly and is routed to the BMC. The BMC debounces and monitors the signal. The signal must be in a constant state for 8 ms before it is treated as asserted. 56 Revision 1.3 Intel order number E15331-006