Intel X38ML Product Specification - Page 110

POST Code Checkpoints

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 110 highlights

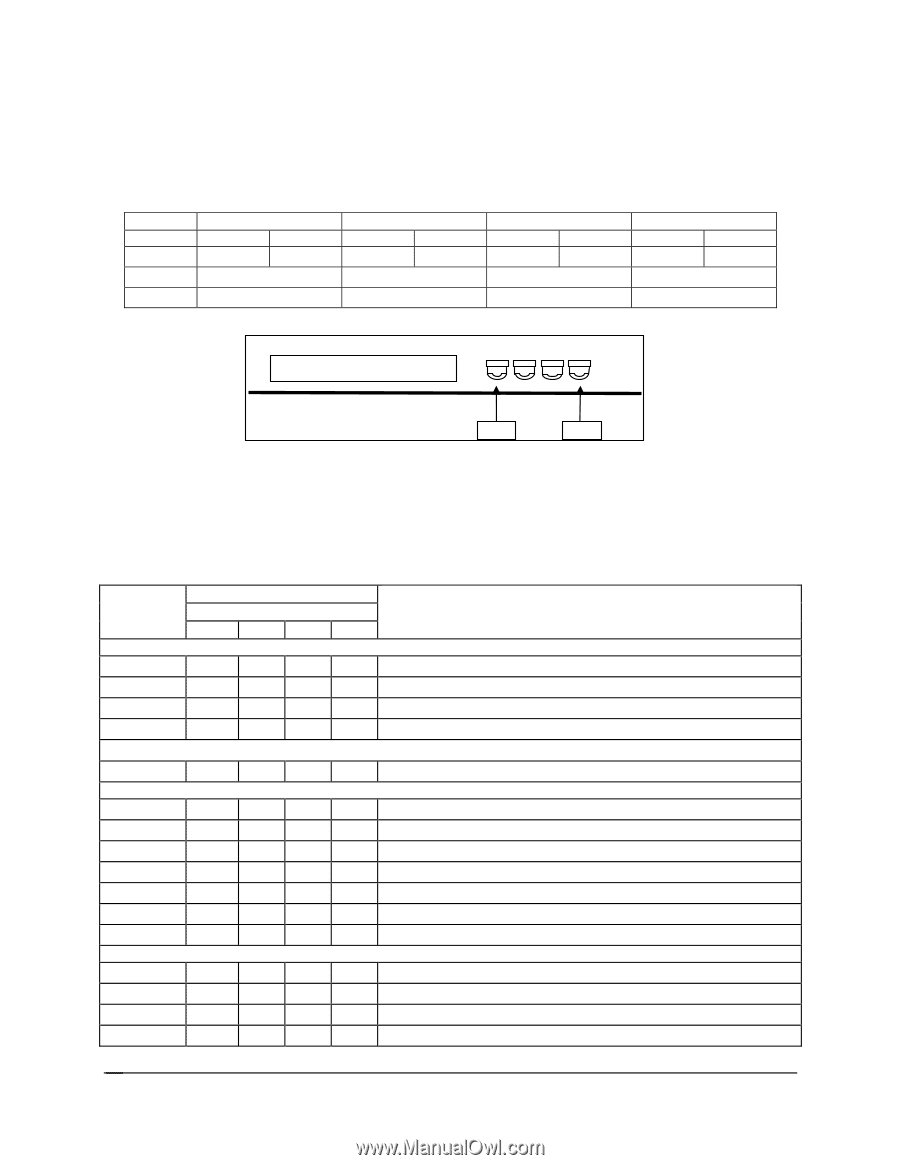

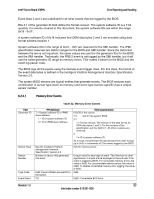

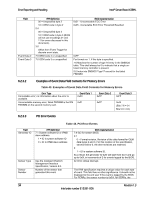

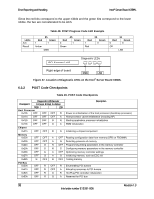

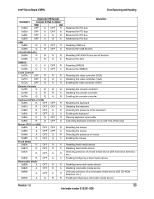

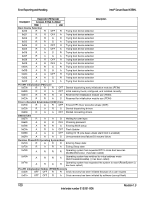

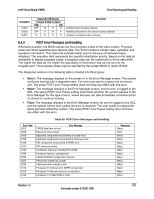

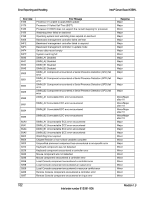

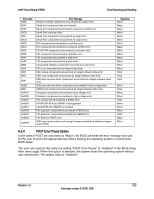

Error Reporting and Handling Intel® Server Board X38ML Since the red bits correspond to the upper nibble and the green bits correspond to the lower nibble, the two are concatenated to be ACh. LEDs Ach Result Table 48. POST Progress Code LED Example 8h Red Green 1 1 Amber MSB Red 0 Green 4h Green 1 Red 1 Red 2h Green 0 1h Red Green 0 0 Off LSB PCI Express* x16 Diagnostic LEDs Right edge of board MSB LSB Figure 27. Location of Diagnostic LEDs on the Intel® Server Board X38ML 6.3.2 POST Code Checkpoints Table 49. POST Code Checkpoints Diagnostic LED Decoder Checkpoint G=Green, R=Red, A=Amber MSB LSB Host Processor 0x10h OFF OFF OFF R 0x11h OFF OFF OFF A 0x12h OFF OFF G R 0x13h OFF OFF G A Chipset 0x21h OFF OFF R G Memory 0x22h OFF OFF A OFF 0x23h OFF OFF A G 0x24h OFF G R OFF 0x25h OFF G R G 0x26h OFF G A OFF 0x27h OFF G A G 0x28h G OFF R OFF PCI Bus 0x50h OFF R OFF R 0x51h OFF R OFF A 0x52h OFF R G R 0x53h OFF R G A Description Power-on initialization of the host processor (bootstrap processor) Host processor cache initialization (including AP) Starting application processor initialization SMM initialization Initializing a chipset component Reading configuration data from memory (SPD on FBDIMM) Detecting presence of memory Programming timing parameters in the memory controller Configuring memory parameters in the memory controller Optimizing memory controller settings Initializing memory, such as ECC init Testing memory Enumerating PCI busses Allocating resources to PCI busses Hot-Plug PCI controller initialization Reserved for PCI bus 98 Revision 1.3 Intel order number E15331-006