Intel X38ML Product Specification - Page 85

User Model, Sessions, Media Bridging, Request/Response Protocol, Host to BMC Communication Interface

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 85 highlights

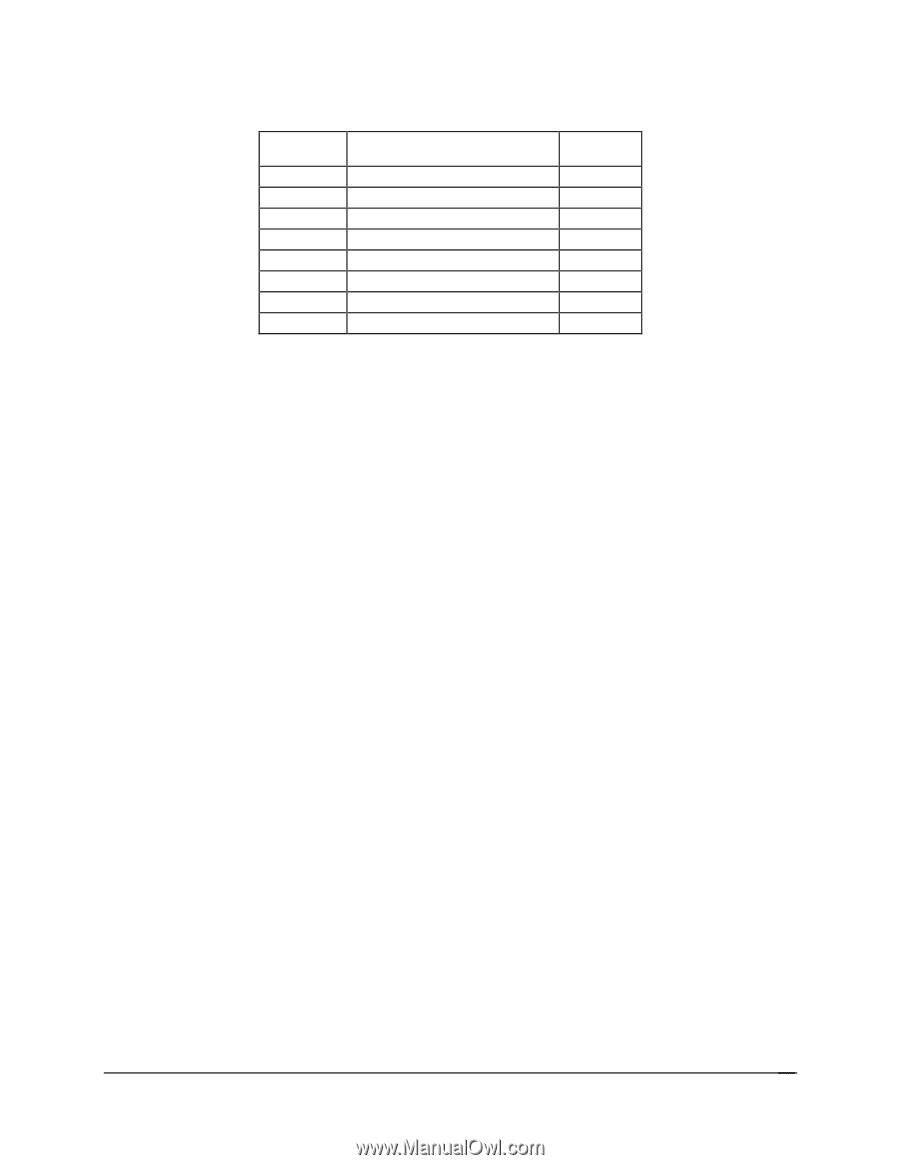

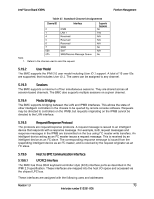

Intel® Server Board X38ML Platform Management Table 37. Standard Channel Assignments Channel ID Interface Note: 1. 0 IPMB 1 LAN 1 4 Reserved 5 Reserved 6 Reserved 7 SMM 0Eh Self 1 0Fh SMS/Receive Message Queue Refers to the channel used to send the request. Supports Sessions No Yes N/A N/A N/A No N/A No 5.19.2 User Model The BMC supports the IPMI 2.0 user model including User ID 1 support. A total of 15 user IDs are supported, that includes User ID 1. The users can be assigned to any channel. 5.19.3 Sessions The BMC supports a maximum of four simultaneous sessions. They are shared across all session-based channels. The BMC also supports multiple sessions on a given channel. 5.19.4 Media Bridging The BMC supports bridging between the LAN and IPMB interfaces. This allows the state of other intelligent controllers in the chassis to be queried by remote console software. Requests may be directed to controllers on the IPMB, but requests originating on the IPMB cannot be directed to the LAN interface. 5.19.5 Request/Response Protocol The protocols are request/response protocols. A request message is issued to an intelligent device that responds with a response message. For example, both request messages and response messages in the IPMB are transmitted on the bus using I2C master write transfers. An intelligent device acting as an I2C master issues a request message. This is received by an intelligent device as an I2C slave. The corresponding response message is issued from the responding intelligent device as an I2C master, and is received by the request originator as an I2C slave. 5.19.6 Host to BMC Communication Interface 5.19.6.1 LPC/KCS Interface The BMC has three 8042 keyboard controller style (KCS) interface ports as described in the IPMI 2.0 specification. These interfaces are mapped into the host I/O space and accessed via the chipset LPC bus. These interfaces are assigned with the following uses and addresses: Revision 1.3 73 Intel order number E15331-006