Intel X38ML Product Specification - Page 83

Power Unit Management

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 83 highlights

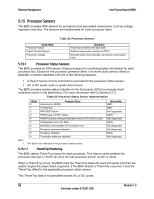

Intel® Server Board X38ML Platform Management OEM SDR records are used to configure which temperature sensors are associated with which fan control domains and the algorithmic relationship between the temperature and fan speed. Multiple OEM SDRs can reference or control the same fan control domain, and multiple OEM SDRs can reference the same temperature sensors. The PWM duty-cycle value for a domain is computed as a percentage using one or more instances of a stepwise linear algorithm and a clamp algorithm. The transition from one computed nominal fan speed (PWM value) to another is ramped over time to minimize audible transitions. The ramp rate is configurable via the OEM SDR. You can define multiple stepwise linear and clamp controls for each fan domain and used simultaneously. For each domain, the BMC uses the maximum of the domain's stepwise linear control contributions and the sum of the domain's clamp control contributions to compute the domain's PWM value, except you can configure a stepwise linear instance to provide the domain maximum. Hysteresis can be specified to minimize fan speed oscillation and to smooth fan speed transitions. If a legacy Tcontrol SDR format does not allow specifying hysteresis, the BMC assumes a hysteresis value of zero. 5.16.3 Thermal and Acoustic Management This feature refers to enhanced fan management to keep the system optimally cooled while reducing the amount of noise generated by the system fans. Aggressive acoustics standards might require a trade-off between fan speed and system performance parameters that contribute to the cooling requirements, primarily memory bandwidth. The BIOS, BMC, and SDRs work together to control and determine the trade-off. 5.17 Power Unit Management The BMC supports an IPMI type 09h, or power unit sensor, using the following offsets: Event Offset Trigger 00h 04h 05h Meaning Power off AC lost Soft power control failure 5.17.1 Power Off The BMC asserts the Power Off offset whenever the system DC power is off. 5.17.2 AC Lost The BMC asserts the AC lost offset when AC power is applied to the system and the previous system power state was on. This offset is used for event generation only and does not remain asserted. 5.17.3 Soft Power Control Fault The BMC asserts the Soft Power Control Failure offset if the system fails to power-on within 8 seconds due to the following power control sources: Revision 1.3 71 Intel order number E15331-006