Intel X38ML Product Specification - Page 72

BMC Reset Control, System Initialization

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 72 highlights

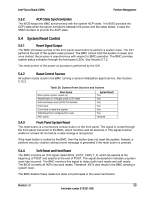

Platform Management Intel® Server Board X38ML 5.4.5 BMC Command Used to Reset System Chassis Control is the primary command used to reset the system. 5.4.6 Watchdog Timer Expiration You can configure the watchdog timer to cause a system reset when the timer expires. See the Intelligent Platform Management Interface Specification, Version 2.0. 5.5 BMC Reset Control Table 30. BMC Reset Sources and Actions Reset Source Standby power comes up BMC completes standard firmware update BMC IPMI watchdog timer reset System Reset? No (system is not up yet) No Yes (if configured) BMC Reset Yes Yes No 5.5.1 BMC Exits Firmware Update When completing a firmware update, the BMC resets. The BMC re-synchronizes to the state of the processor and power control signals it finds when it initializes. 5.5.2 Standby Power Comes Up The system has AC power applied, but the system is not up. The BMC resets when DC power output from the power supplies is available. The BMC re-synchronizes to the state of the processor and power control signals it finds when it initializes. 5.6 System Initialization The following items are initialized by both the BIOS and the BMC during system initialization. 5.6.1 Processor TControl Setting Processors used with this chipset implement a feature called Tcontrol, which provides a processor-specific value that can be used to adjust the fan control behavior to achieve optimum cooling and acoustics. The BMC cannot access these values. The BIOS reads the values during POST and communicates them to the BMC using the Set Processor Tcontrol command. The BMC uses these values as part of the fan speed control algorithm. 5.6.2 Fault Resilient Booting (FRB) Fault resilient booting (FRB) is a set of BIOS and BMC algorithms and hardware support that allow a multiprocessor system to boot even if the bootstrap processor (BSP) fails. Only FRB2 is supported, using watchdog timer commands. FRB2 refers to the FRB algorithm that detects system failures during the POST. The BIOS uses the BMC watchdog timer to back up its operation during POST. The BIOS configures the watchdog timer to indicate the BIOS is using the timer for the FRB2 phase of the boot operation. 60 Revision 1.3 Intel order number E15331-006