Intel X38ML Product Specification - Page 30

Super I/O Chip

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

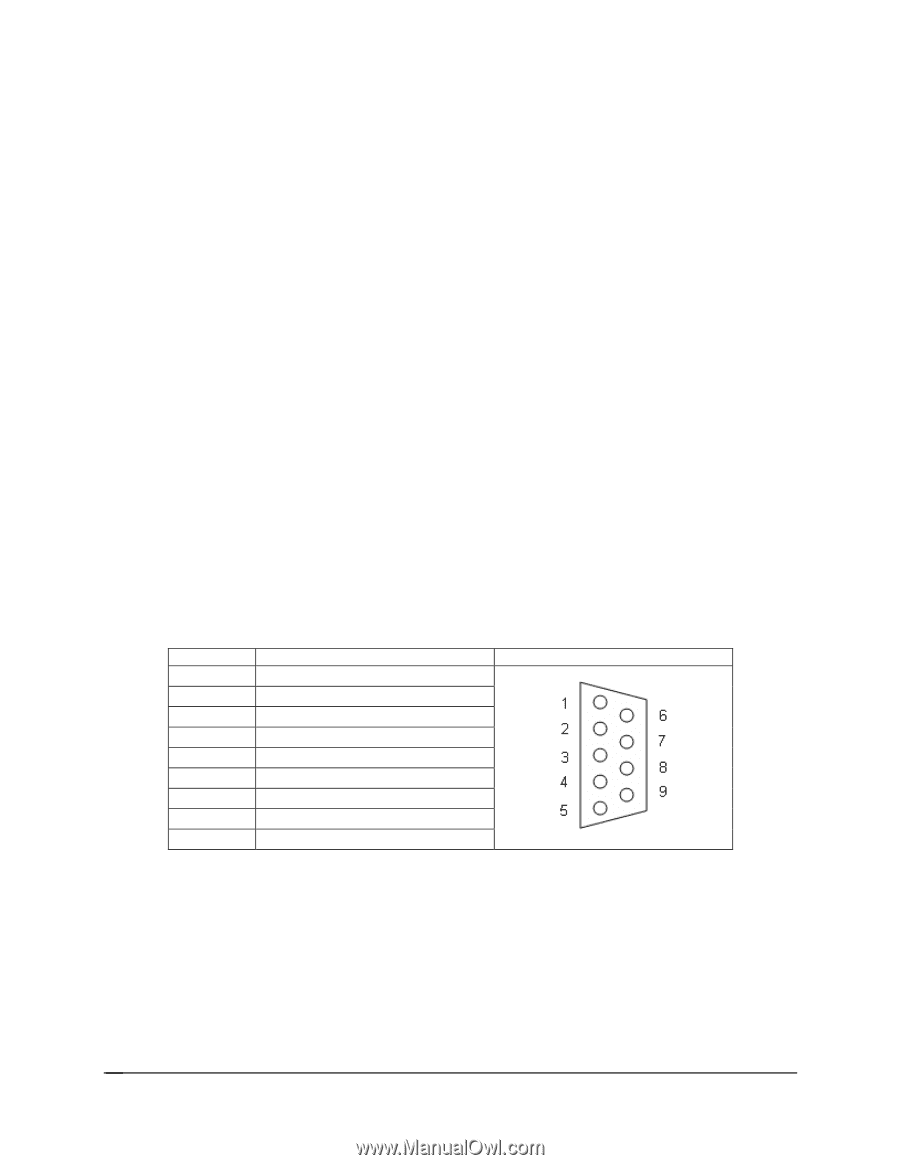

Functional Architecture Intel® Server Board X38ML baseboard. One 10-pin internal on-board header is provided which is capable of supporting two additional USB 2.0 ports. 3.5.6 Super I/O Chip The Super I/O chip integrated into the Integrated BMC provides legacy I/O support. The Super I/O chip contains the necessary circuitry to support two serial ports and hardware control/monitor functions. The server board implements the following features: ƒ Two fully functional serial ports, compatible with the 16C550 ƒ Up to 16 shared GPIO ports ƒ Programmable wake-up event support ƒ Plug and play register set ƒ Power supply control ƒ Watchdog timer compliant with Microsoft SHDG* ƒ LPC to SPI bridge for system BIOS support ƒ Real-time clock module with the external RTC interface 3.5.6.1 Serial Ports The board provides two serial ports. Serial A is a standard DB-9 interface located at the rear I/O panel of the server board next to the video connector. The reference designator is J5A1. Serial B is a 3-pin header interface located near the CMOS battery. The reference designator is J4C1. Pin 1 2 3 4 5 6 7 8 9 DCD RXD TXD DTR GND DSR RTS CTS RI Table 2. Serial A Header Pin-out Signal Name Serial Port A Header Pin-out 18 Revision 1.3 Intel order number E15331-006