Intel X38ML Product Specification - Page 107

Examples of Event Data Field Contents for PCI Errors, 2.3.5, FRB-2 Error Events

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

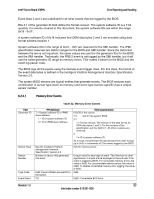

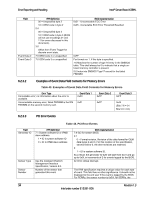

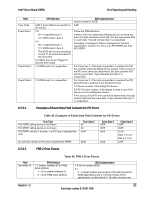

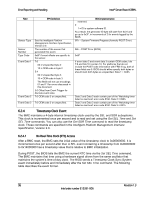

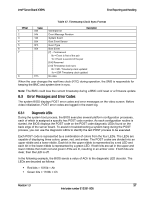

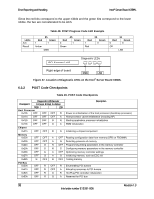

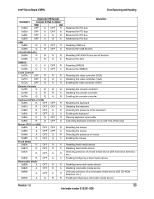

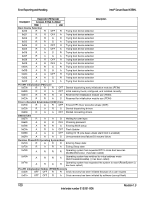

Page 107 highlights

Intel® Server Board X38ML Error Reporting and Handling Field Type Code Event Data 1 Event Data 2 Event Data 3 IPMI Definition 0x6F if event offsets are specific to the sensor 7:6 00 = unspecified byte 2 10 = OEM code in byte 2 5:4 00 = unspecified byte 3 10 = OEM code in byte 3 The BIOS will not use encodings 01 and 11 for errors discussed in this document 3:0 Offset from Event Trigger for discrete event state. 7:0 OEM code 2 or unspecified. 7:0 OEM code 3 or unspecified. BIOS Implementation sensor number is 0xEB. 0x6F Follow the IPMI definition. If either of the two data bytes following this do not have any data, that byte should be set to 0xff, and the appropriate field in event data 1 should indicate that it is unspecified. According to Intelligent Platform Management Interface Specification, Version 2.0, 3:0 is 4 for PCI PERR and 5 for PCI SERR. For format rev 0, if this byte is specified, it contains the PCI bus number where the failing device resides. If the source of the PCI error cannot be determined, this byte contains 0xff and the event data 1 byte indicates that byte 2 is unspecified. For format rev 0, if this byte is specified, it contains the PCI device/function address in the standard format: 7:3 Device number of the failing PCI device. 2:0 PCI function number. It will always contain a zero if the device is not a multifunction device. If the source of the PCI error cannot be determined, this byte contains 0xff and the event data 1 byte indicates that byte 3 is unspecified. 6.2.3.4 Examples of Event Data Field Contents for PCI Errors Table 45. Examples of Event Data Field Contents for PCI Errors Error Type PCI PERR, failing device is not known PCI SERR, failing device is not known PCI PERR, device 3, function 1 on PCI bus 5 reported the error Event Data 1 04 05 0xA4 An unknown device on PCI bus 0 reported the SERR 0x85 Event Data 2 0xFF 0xFF 0x05 0x00 Event Data 3 0xFF 0xFF 0x19 (Bits 7:3 = 03 Bits 2:0 = 01) 0xFF 6.2.3.5 FRB-2 Error Events Table 46. FRB-2 Error Events Field Generator ID IPMI Definition 7:1 System software ID or IPMB slave address. 1 = ID is system software ID 0 = ID is IPMB slave address BIOS Implementation 7:4 0x3 for system BIOS. 3:1 0 = Format revision and revision of the data format for OEM data bytes 2 and 3. For this revision of the specification, set this field to 0. All other revisions are Revision 1.3 95 Intel order number E15331-006