Intel X38ML Product Specification - Page 86

Get Status/Abort, Set BMC Global Enables, 0CA2h - 0CA3h, Intelligent Platform Management, Interface

|

UPC - 735858197397

View all Intel X38ML manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 86 highlights

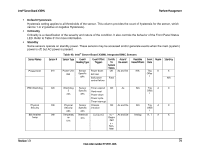

Platform Management Intel® Server Board X38ML Table 38. Keyboard Controller Style Interfaces Name SMS Interface SMM Interface Use SMS, BIOS POST, and utility access SMI handling for error logging Address 0CA2h - 0CA3h 0CA4h - 0CA5h The BMC gives higher priority to transfers that take place using the server management mode (SMM) interface. This provides minimum latency during SMI accesses. The BMC acts as a bridge between the server management software (SMS) and the IPMB interfaces. Interface registers provide a mechanism for communications between the BMC and the host system. Most platforms implement the interfaces as host I/O space mapped registers. The interfaces consist of three sets of two 1-byte-wide registers. 5.19.6.2 Receive Message Queue The receive message queue is only accessible via the SMS interface since that interface is the BMC's host/system interface. The queue is two entries in size. Per-channel queue slots are not provided. 5.19.6.3 SMS/SMM Status Register Bits in the status register provide interface and protocol state information. As an extension to the IPMI 2.0 KCS interface definition, the OEM1 and OEM2 bits in the SMS and SMM interfaces are defined to provide BMC status information. 5.19.6.4 Server Management Software (SMS) Interface The SMS interface is the BMC host interface. The BMC implements the SMS KCS interface as described in the IPMI 2.0 specification. The BMC implements the optional Get Status/Abort transaction on this interface. Only logical unit number (LUN) 0 is supported on this interface. The status register OEM1/2 bits are in Section 5.19.6.3 If the BMC is configured using the Set BMC Global Enables command, it can generate an interrupt requesting attention when setting the SMS_ATN bit in the status register. The SMS_ATN bit that is set indicates one or more of the following: ƒ At least one message is in the BMC receive message queue ƒ An event is in the event message buffer ƒ The Watchdog pre-timeout interrupt flag has been set All conditions must be cleared and all BMC to SMS messages must be flushed for the SMS_ATN bit to be cleared. The host I/O address of the SMS interface is nominally 0CA2h - 0CA3h, but this address assignment may be overridden. See the platform-specific information in the Appendix. The operation of the SMS interface is described in the Intelligent Platform Management Interface Specification. See the chapter titled, "Keyboard Controller Style (KCS) Interface." 74 Revision 1.3 Intel order number E15331-006