Nintendo 1504166 Programming Manual - Page 110

DMA Control, Note], DMA0CNT_H [d15] DMA Enable Flag

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 110 highlights

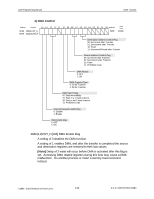

AGB Programming Manual DMA Transfer 4) DMA Control Address 0BAh Register DMA0 CNT_H 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes R/W Initial Value 0000h Destination Address Control Flag 00: Increment after Transfer 01: Decrement after Transfer 10: Fixed 11: Increment/Reload after Transfer Source Address Control Flag 00: Increment after Transfer 01: Decrement after Transfer 10: Fixed 11: Prohibited Code DMA Repeat 0: OFF 1: ON DMA Transfer Type 0: 16-bit Transfer 1: 32-bit Transfer DMA Start Timing 00: Start Immediately 01: Start in a V-blank Interval 10: Start in an H-blank Interval 11: Prohibited Code Interrupt Request Enable Flag 0: Disable 1: Enable DMA Enable Flag 0: OFF 1: ON DMA0CNT_H [d15] DMA Enable Flag A setting of 0 disables DMA. A setting of 1 enables DMA, and after the transfer is completed the source and destination registers are restored to their last values. [Note] Delay of 2 waits will occur before DMA is activated after this flag is set. Accessing DMA related registers during this time may cause a DMA malfunction. Do another process or insert a dummy load command instead. ©1999 - 2001 Nintendo of America Inc. 110 D.C.N. AGB-06-0001-002B4