Nintendo 1504166 Programming Manual - Page 17

Memory Configuration and Access Width, 2.4 Little-Endian, Mask ROM, Flash Memory

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 17 highlights

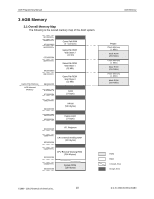

AGB Programming Manual System Configuration 2.3 Memory Configuration and Access Width Memory Type OAM Palette RAM VRAM CPU Internal Working RAM CPU External Working RAM Internal registers Game Pak ROM (Mask ROM, Flash Memory) Game Pak RAM (SRAM, Flash Memory) Bus Width 32 16 16 32 16 32 16 8 DMA Read Write Width Width 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 16/32 -- -- CPU Read Write Width Width 16/32 16/32 16/32 16/32 16/32 16/32 8/16/32 8/16/32 8/16/32 8/16/32 8/16/32 8/16/32 8/16/32 16/32 8 8 Good execution efficiency is obtained when programs that operate from the Game Pak use 16-bit instructions (16-bit compiler), and those that operate from CPU Internal Working RAM use 32-bit instructions (32-bit compiler). 2.4 Little-Endian In the AGB CPU, memory addresses are allocated in 8-bit increments, and littleendian format is used in implementing the 8-, 16-, and 32-bit access widths. 0003h 0002h 0001h 0000h Memory D C B A Register d31 d24 d23 d16 d15 d08 d07 d00 D C B A ©1999 - 2001 Nintendo of America Inc. 17 D.C.N. AGB-06-0001-002B4