Nintendo 1504166 Programming Manual - Page 30

OBJ Character VRAM Mapping Format, H-Blank Interval OBJ Processing Flag

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

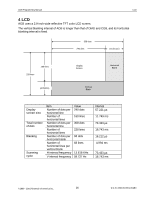

AGB Programming Manual Image System DISPCNT [d07] Forced Blank Setting this bit causes the CPU to forcibly halt operation of the image processing circuit, allowing access to VRAM, color palette RAM, OAM, and the internal registers. The LCD screen displays white during a forced blank. However, the internal HV synchronous counter continues to operate even during a forced blank. When the internal HV synchronous counter cancels a forced blank during a display period, the display begins from the beginning, following the display of three vertical lines. DISPCNT [d06] OBJ Character VRAM Mapping Format Specifies the VRAM mapping format for an OBJ character. A setting of 0 causes the OBJ character to be handled in memory mapped 2-dimensional. A setting of 1 causes the OBJ character to be handled in memory mapped 1-dimensional. For information on OBJ character VRAM mapping formats, see section 6.3.2, Character Data Mapping. DISPCNT [d05] H-Blank Interval OBJ Processing Flag A setting of 0 executes OBJ Render Processing with all H-Line intervals(including H-Blank intervals). A setting of 1 executes OBJ Render Processing with the display intervals only and not for H-Blank intervals. Thus, when the user accesses OAM or OBJ VRAM during an H-Blank interval, this bit needs to be set. However, also in this situation, maximum OBJ display performance cannot be obtained. DISPCNT [d04] Display Frame Selection When rendering in bitmap format in a mode in which there are 2 frame buffers (BG modes 4 and 5), this bit allows selection of one of the frame buffers for rendering. A setting of 0 selects the contents of frame buffer 0 for rendering; a setting of 1 selects the contents of frame buffer 1 for rendering. DISPCNT [d03] (CGB Mode) AGB is equipped with 2 CPUs. In AGB mode, a 32-bit RISC CPU starts, and in CGB mode, an 8-bit CISC CPU starts. Because this bit is controlled by the system, it cannot be accessed by the user. DISPCNT [d02-00] BG Mode Selects the BG mode from a range of 0-5. For more information on BG modes, see the following section. ©1999 - 2001 Nintendo of America Inc. 30 D.C.N. AGB-06-0001-002B4