Nintendo 1504166 Programming Manual - Page 96

Waveform RAM, The Sound 3 circuit plays the waveform data specified by the bank setting

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 96 highlights

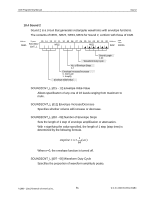

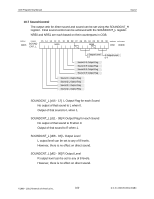

AGB Programming Manual Sound Waveform RAM Waveform RAM consists of a 4-bit x 32-step waveform pattern. It has 2 banks, with [d06] of SOUND3CNT_L used for bank specification. The Sound 3 circuit plays the waveform data specified by the bank setting, while the waveform RAM not specified is the waveform RAM accessed by the user. Address 090h Register WAVE_ RAM0_L 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 2 Step 3 Step 0 Step 1 R/W Initial Value - Address 092h Register WAVE_ RAM0_H 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 6 Step 7 Step 4 Step 5 R/W Initial Value - Address 094h Register WAVE_ RAM1_L 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 10 Step 11 Step 8 Step 9 R/W Initial Value - Address Register 096h WAVE_ RAM1_H 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 14 Step 15 Step 12 Step 13 R/W Initial Value - Address 098h Register WAVE_ RAM2_L 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 18 Step 19 Step 16 Step 17 R/W Initial Value - Address 09Ah Register WAVE_ RAM2_H 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 22 Step 23 Step 20 Step 21 R/W Initial Value - Address 09Ch Register WAVE_ RAM3_L 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 26 Step 27 Step 24 Step 25 R/W Initial Value - Address 09Eh Register WAVE_ RAM3_H 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Step 30 Step 31 Step 28 Step 29 R/W Initial Value - ©1999 - 2001 Nintendo of America Inc. 96 D.C.N. AGB-06-0001-002B4