Nintendo 1504166 Programming Manual - Page 111

DMA0CNT_H [d14] Interrupt Request Enable Flag, DMA0CNT_H [d13 - 12] DMA Startup Timing

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 111 highlights

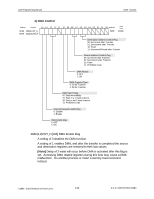

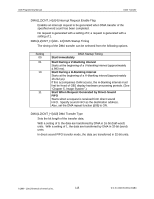

AGB Programming Manual DMA Transfer DMA0CNT_H [d14] Interrupt Request Enable Flag Enables an interrupt request to be generated when DMA transfer of the specified word count has been completed. No request is generated with a setting of 0; a request is generated with a setting of 1. DMA0CNT_H [d13 - 12] DMA Startup Timing The timing of the DMA transfer can selected from the following options. Setting 00 01 10 11 DMA Startup Timing Start immediately Start during a V-blanking interval Starts at the beginning of a V-blanking interval (approximately 4.993 ms). Start during a H-blanking interval Starts at the beginning of a H-blanking interval (approximately 16.212 µs). If this accompanies OAM access, the H-blanking interval must first be freed of OBJ display hardware processing periods. (See "5 Image System".) Prohibited Code DMA0CNT_H [d10] DMA Transfer Type Sets the bit length of the transfer data. With a setting of 0, the data are transferred by DMA in 16-bit (half-word) units. With a setting of 1, the data are transferred by DMA in 32-bit (word) units. DMA0CNT_H [d09] DMA Repeat With the DMA repeat function set to ON, if V-blanking or H-blanking intervals are selected as the timing of DMA startup, DMA is restarted when the next startup condition occurs (a V-blank or H-blank). In this mode, restarting will continue as long as the DMA enable flag is not set to 0. When the DMA repeat function is set to OFF, DMA halts as soon as the amount of data specified by the value in the word-count register has been transferred. ©1999 - 2001 Nintendo of America Inc. 111 D.C.N. AGB-06-0001-002B4