Nintendo 1504166 Programming Manual - Page 15

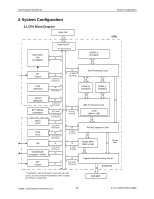

System Configuration, 2.1 CPU Block Diagram

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 15 highlights

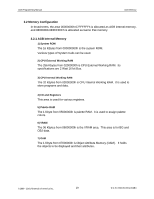

AGB Programming Manual 2 System Configuration 2.1 CPU Block Diagram Game Pak 16 ARM7TDMI CPU (16.78MHz) Game Pak I/F (Prefetch Buffer) 32 System Configuration CPU VRAM_A (64KByte) 16 INT Control ROM (16KByte) 32 R:8/16/32 W:8/16/32 32 R:8/16/32 16 R:16/32 W:16/32 BG Processing Circuit 16 16 VRAM_B (16KByte) VRAM_C (16KByte) 16 16 16 16 16 16 16 WRAM (32KByte) EXT. WRAM (256KByte) DMAC (4ch) Timer (4ch) SIO SOUND(CGB compatible + PWM) 32 R:8/16/32 W:8/16/32 16(2 Wait) R:8/16/32 W:8/16/32 32 R:8/16/32 W:8/16/32 32 R:8/16/32 W:8/16/32 32 R:8/16/32 W:8/16/32 32 KEY Control 32 32 32 R:16/32 W:16/32 OBJ Processing Circuit OAM (64bit x 128) 32 R:16/32 W:16/32 Priority Evaluation Circuit 16 R:16/32 W:16/32 Palette RAM (16bit x 512) Bitmap Mode 32 R:8/16/32 W:8/16/32 Special Color Processing Circuit RGB(5:5:5) 16 * "R:8/16/32" and "W:8/16/32" mean that you can access an area of 8bits/16bits/32bits when reading and writing, respectively. LCD Unit ©1999 - 2001 Nintendo of America Inc. 15 D.C.N. AGB-06-0001-002B4