Nintendo 1504166 Programming Manual - Page 113

DMA 1 and 2, Thus, in 16-bit data transfer mode, up to 4000h x 2=8000h bytes can

|

View all Nintendo 1504166 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 113 highlights

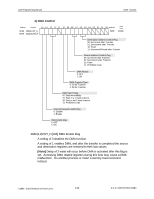

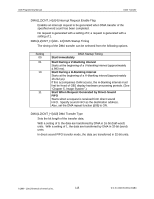

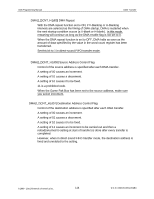

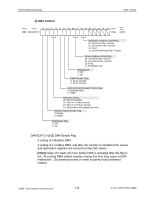

AGB Programming Manual DMA Transfer 12.2 DMA 1 and 2 DMA channels 1 and 2 provide access between the Game Pak bus/internal memory of the main unit and internal memory of the main unit, or between the Game Pak bus/internal memory of the main unit and the direct sound FIFO. Transfers to directsound FIFO can be accomplished only by using DMA 1 and 2. 1) Source Address Specifies the source address using 28 bits. The area 00000000h-0FFFFFFFh can be specified. Address Register 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes 0BCh DMA1SAD_L 0C8h DMA2SAD_L W Initial Value 0000h Address Register 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Initial Value 0BEh DMA1SAD_H 0CAh DMA2SAD_H W 0000h 2) Destination Address Specifies the destination address using 27 bits. The area 00000000h-07FFFFFFh (internal memory area of main unit) can be specified. Address Register 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Initial Value 0C0h DMA1DAD_L 0CCh DMA2DAD_L W 0000h Address Register 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Initial Value 0C2h DMA1DAD_H W 0000h 0CEh DMA2DAD_H 3) Word Count Specifies the number of bytes transferred by DMA 1 and DMA 2, using 14 bits. The number can be specified in the range 0001h~3FFFh~0000h (when 0000h is set, 4000h bytes are transferred). Thus, in 16-bit data transfer mode, up to 4000h x 2=8000h bytes can be transferred, and in 32-bit data transfer mode, up to 4000h x 4=10000h bytes can be transferred. Address Register 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00 Attributes Initial Value 0C4h DMA1CNT_L 0D0h DMA2CNT_L W 0000h The word-count register setting is disabled in direct-sound FIFO transfer mode. With each request received from sound FIFO, 32 bits x 4 words of sound data are transferred. ©1999 - 2001 Nintendo of America Inc. 113 D.C.N. AGB-06-0001-002B4