AMD AMD-K6-2/500AFX Data Sheet - Page 27

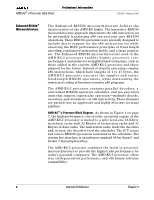

Internal Architecture, AMD-K6, 2 Processor Data Sheet, Processor Block Diagram

|

View all AMD AMD-K6-2/500AFX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 27 highlights

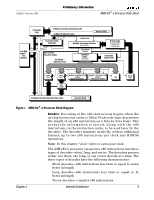

21850J/0-February 2000 Preliminary Information AMD-K6®-2 Processor Data Sheet 100 MHz Super7™ Bus Interface Predecode Logic 32-KByte Level-One Instruction Cache 20-KByte Predecode Cache 64-Entry ITLB Level-One Cache Controller Out-of-Order Execution Engine Six RISC86 ® Operation Issue 16-Byte Fetch Multiple Instruction Decoders x86 to RISC86 Four RISC86 Decode Scheduler Buffer (24 RISC86) Branch Logic (8192-Entry BHT) (16-Entry BTC) (16-Entry RAS) Instruction Control Unit Load Store Register X Functional Units Register Y Functional Units Unit Unit Integer/ Integer/ FPU Multimedia/3DNow!™ Multimedia /3DNow! Store Queue Branch Unit 32-KByte Level-One Dual-Port Data Cache 128-Entry DTLB Figure 1. AMD-K6®-2 Processor Block Diagram Decoders. Decoding of the x86 instructions begins when the on-chip instruction cache is filled. Predecode logic determines the length of an x86 instruction on a byte-by-byte basis. This predecode information is stored, along with the x86 instructions, in the instruction cache, to be used later by the decoders. The decoders translate on-the-fly, with no additional latency, up to two x86 instructions per clock into RISC86 operations. Note: In this chapter, "clock" refers to a processor clock. The AMD-K6-2 processor categorizes x86 instructions into three types of decodes-short, long, and vector. The decoders process either two short, one long, or one vector decode at a time. The three types of decodes have the following characteristics: s Short decodes-x86 instructions less than or equal to seven bytes in length s Long decodes-x86 instructions less than or equal to 11 bytes in length s Vector decodes-complex x86 instructions Chapter 2 Internal Architecture 7