AMD AMD-K6-2/500AFX Data Sheet - Page 30

Prefetching, Predecode Bits, Cache Sector Organization - architecture

|

View all AMD AMD-K6-2/500AFX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

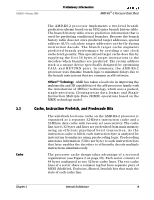

AMD-K6®-2 Processor Data Sheet Preliminary Information 21850J/0-February 2000 Prefetching Predecode Bits Two forms of cache misses and associated cache fills can take place-a tag-miss cache fill and a tag-hit cache fill. In the case of a tag-miss cache fill, the miss is due to a tag mismatch, in which case the required cache line is filled from external memory, and the cache line within the sector that was not required is marked as invalid. In the case of a tag-hit cache fill, the address matches the tag, but the requested cache line is marked as invalid. The required cache line is filled from external memory, and the cache line within the sector that is not required remains in the same cache state. The AMD-K6-2 processor conditionally performs cache prefetching which results in the filling of the required cache line first, and a prefetch of the second cache line making up the other half of the sector. From the perspective of the external bus, the two cache-line fills typically appear as two 32-byte burst read cycles occurring back-to-back or, if allowed, as pipelined cycles. The 3DNow! technology includes an instruction called PREFETCH that allows a cache line to be prefetched into the data cache. The PREFETCH instruction format is defined in Table 17, "3DNow!™ Instructions," on page 81. For more detailed information, see the 3DNow!™ Technology Manual, order# 21928. Decoding x86 instructions is particularly difficult because the instructions are variable-length and can be from 1 to 15 bytes long. Predecode logic supplies the five predecode bits that are associated with each instruction byte. The predecode bits indicate the number of bytes to the start of the next x86 instruction. The predecode bits are stored in an extended instruction cache alongside each x86 instruction byte as shown in Figure 2. The predecode bits are passed with the instruction bytes to the decoders where they assist with parallel x86 instruction decoding. Tag Address Cache Line 0 Byte 31 Predecode Bits Byte 30 Predecode Bits Byte 0 Predecode Bits MESI Bits Cache Line 1 Byte 31 Predecode Bits Byte 30 Predecode Bits Byte 0 Predecode Bits MESI Bits Figure 2. Cache Sector Organization 10 Internal Architecture Chapter 2