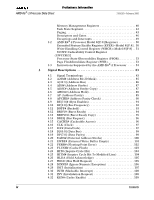

Contents

v

21850J/0—February 2000

AMD-K6

®

-2 Processor Data Sheet

Preliminary Information

4.33

LOCK# (Bus Lock)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

4.34

M/IO# (Memory or I/O)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

4.35

NA# (Next Address) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 112

4.36

NMI (Non-Maskable Interrupt) . . . . . . . . . . . . . . . . . . . . . . . 112

4.37

PCD (Page Cache Disable)

. . . . . . . . . . . . . . . . . . . . . . . . . . 113

4.38

PCHK# (Parity Check) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

4.39

PWT (Page Writethrough) . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.40

RESET (Reset)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

4.41

RSVD (Reserved) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

4.42

SCYC (Split Cycle) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

4.43

SMI# (System Management Interrupt)

. . . . . . . . . . . . . . . . 117

4.44

SMIACT# (System Management Interrupt Active)

. . . . . . 118

4.45

STPCLK# (Stop Clock) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

4.46

TCK (Test Clock)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

4.47

TDI (Test Data Input)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

4.48

TDO (Test Data Output)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

4.49

TMS (Test Mode Select)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

4.50

TRST# (Test Reset)

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

4.51

VCC2DET (V

CC2

Detect) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

4.52

VCC2H/L# (V

CC2

High/Low)

. . . . . . . . . . . . . . . . . . . . . . . . . 121

4.53

W/R# (Write/Read) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

4.54

WB/WT# (Writeback or Writethrough)

. . . . . . . . . . . . . . . . 123

5

Bus Cycles

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.1

Timing Diagrams

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.2

Bus State Machine Diagram

. . . . . . . . . . . . . . . . . . . . . . . . . 129

Idle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Data-NA# Requested. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Pipeline Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

Pipeline Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

Transition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

5.3

Memory Reads and Writes

. . . . . . . . . . . . . . . . . . . . . . . . . . 132

Single-Transfer Memory Read and Write . . . . . . . . . . . . . . . 132

Misaligned Single-Transfer Memory Read and Write . . . . . 134

Burst Reads and Pipelined Burst Reads . . . . . . . . . . . . . . . . 136

Burst Writeback. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

5.4

I/O Read and Write

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Basic I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140

Misaligned I/O Read and Write . . . . . . . . . . . . . . . . . . . . . . . 141

5.5

Inquire and Bus Arbitration Cycles

. . . . . . . . . . . . . . . . . . . 142

Hold and Hold Acknowledge Cycle . . . . . . . . . . . . . . . . . . . . 142

HOLD-Initiated Inquire Hit to Shared or Exclusive Line . . 144

HOLD-Initiated Inquire Hit to Modified Line . . . . . . . . . . . 146

AHOLD-Initiated Inquire Miss. . . . . . . . . . . . . . . . . . . . . . . . 148

AHOLD-Initiated Inquire Hit to Shared or Exclusive Line. 150