AMD AMD-K6-2/500AFX Data Sheet - Page 32

Instruction Decode, AMD-K6, 2 Processor Decode Logic

|

View all AMD AMD-K6-2/500AFX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 32 highlights

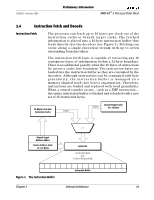

AMD-K6®-2 Processor Data Sheet Preliminary Information 21850J/0-February 2000 Instruction Decode The AMD-K6-2 processor decode logic is designed to decode multiple x86 instructions per clock (see Figure 4). The decode logic accepts x86 instruction bytes and their predecode bits from the instruction buffer, locates the actual instruction boundaries, and generates RISC86 operations from these x86 instructions. RISC86 operations are fixed-length internal instructions. Most RISC86 operations execute in a single clock. RISC86 operations are combined to perform every function of the x86 instruction set. Some x86 instructions are decoded into as few as zero RISC86 operations - for instance a NOP - or one RISC86 operation - a register-to-register add. More complex x86 instructions are decoded into several RISC86 operations. Instruction Buffer On-Chip ROM Short Decoder #1 Short Decoder #2 Long Decoder Vector Decoder RISC86® Sequencer Vector Address Figure 4. AMD-K6®-2 Processor Decode Logic 12 Internal Architecture 4 RISC86 Operations Chapter 2