AMD AMD-K6-2/500AFX Data Sheet - Page 36

Register X and Y Pipelines, 3DNow! ALU, the MMX/3DNow! multiplier and MMX shifter - + multiplier

|

View all AMD AMD-K6-2/500AFX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 36 highlights

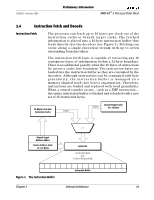

AMD-K6®-2 Processor Data Sheet Preliminary Information 21850J/0-February 2000 Register X and Y Pipelines 16 The Integer X execution unit can operate on all ALU operations, multiplies, divides (signed and unsigned), shifts, and rotates. The Integer Y execution unit can operate on the basic word and doubleword ALU operations - ADD, AND, CMP, OR, SUB, XOR, zero-extend and sign-extend operands. Table 1. Execution Latency and Throughput of Execution Units Functional Unit Function Latency Throughput LEA/PUSH, Address (Pipelined) 1 1 Store Memory Store (Pipelined) 1 1 Load Memory Loads (Pipelined) 2 1 Integer ALU 1 1 Integer X Integer Multiply 2-3 2-3 Integer Shift 1 1 Multimedia MMX ALU (processes MMX Shifts, Packs, Unpack MMX instructions) MMX Multiply 1 1 1 1 2 1 Integer Y Basic ALU (16-bit and 32-bit operands) 1 1 Branch Resolves Branch Conditions 1 1 FPU FADD, FSUB, FMUL 2 2 3DNow! ALU 2 1 3DNow! 3DNow! Multiply 2 1 3DNow! Convert 2 1 The functional units that execute MMX and 3DNow! instructions share pipeline control with the Integer X and Integer Y units. The register X and Y functional units are attached to the issue bus for the register X execution pipeline or the issue bus for the register Y execution pipeline or both. Each register pipeline has dedicated resources that consist of an integer execution unit and an MMX ALU execution unit, therefore allowing superscalar operation on integer and MMX instructions. In addition, both the X and Y issue buses are connected to the 3DNow! ALU, the MMX/3DNow! multiplier and MMX shifter, which allows the appropriate RISC86 operation to be issued through either bus. Figure 6 on page 17 shows the details of the X and Y register pipelines. Internal Architecture Chapter 2