Datasheet

3

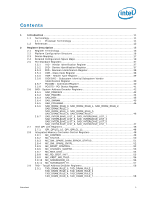

Contents

1

Introduction

............................................................................................................

11

1.1

Terminology

.....................................................................................................

11

1.1.1

Processor Terminology

..........................................................................

11

1.2

References

.......................................................................................................

13

2

Register Description

................................................................................................

15

2.1

Register Terminology

.........................................................................................

15

2.2

Platform Configuration Structure

.........................................................................

16

2.3

Device Mapping

.................................................................................................

17

2.4

Detailed Configuration Space Maps

......................................................................

19

2.5

PCI Standard Registers

......................................................................................

37

2.5.1

VID - Vendor Identification Register

........................................................

37

2.5.2

DID - Device Identification Register

.........................................................

37

2.5.3

RID - Revision Identification Register

.......................................................

38

2.5.4

CCR - Class Code Register

.....................................................................

38

2.5.5

HDR - Header Type Register

...................................................................

39

2.5.6

SID/SVID - Subsystem Identity/Subsystem Vendor

Identification Register

...........................................................................

39

2.5.7

PCICMD - Command Register

.................................................................

40

2.5.8

PCISTS - PCI Status Register

..................................................................

41

2.6

SAD - System Address Decoder Registers

.............................................................

42

2.6.1

SAD_PAM0123

.....................................................................................

42

2.6.2

SAD_PAM456

.......................................................................................

44

2.6.3

SAD_HEN

............................................................................................

45

2.6.4

SAD_SMRAM

........................................................................................

45

2.6.5

SAD_PCIEXBAR

....................................................................................

46

2.6.6

SAD_DRAM_RULE_0, SAD_DRAM_RULE_1, SAD_DRAM_RULE_2,

SAD_DRAM_RULE_3

SAD_DRAM_RULE_4, SAD_DRAM_RULE_5

SAD_DRAM_RULE_6, SAD_DRAM_RULE_7

...............................................

46

2.6.7

SAD_INTERLEAVE_LIST_0, SAD_INTERLEAVE_LIST_1

SAD_INTERLEAVE_LIST_2, SAD_INTERLEAVE_LIST_3

SAD_INTERLEAVE_LIST_4, SAD_INTERLEAVE_LIST_5

SAD_INTERLEAVE_LIST_6, SAD_INTERLEAVE_LIST_7

...............................

47

2.7

Intel QPI Link Registers

......................................................................................

48

2.7.1

QPI_QPILCL_L0, QPI_QPILCL_L1

............................................................

48

2.8

Integrated Memory Controller Control Registers

....................................................

48

2.8.1

MC_CONTROL

......................................................................................

48

2.8.2

MC_STATUS

.........................................................................................

50

2.8.3

MC_SMI_SPARE_DIMM_ERROR_STATUS

..................................................

51

2.8.4

MC_SMI_SPARE_CNTRL

.........................................................................

52

2.8.5

MC_RESET_CONTROL

............................................................................

52

2.8.6

MC_CHANNEL_MAPPER

..........................................................................

53

2.8.7

MC_MAX_DOD

......................................................................................

54

2.8.8

MC_RD_CRDT_INIT

...............................................................................

55

2.8.9

MC_CRDT_WR_THLD

.............................................................................

56

2.8.10

MC_SCRUBADDR_LO

.............................................................................

56

2.8.11

MC_SCRUBADDR_HI

.............................................................................

57

2.9

TAD – Target Address Decoder Registers

..............................................................

58

2.9.1

TAD_DRAM_RULE_0, TAD_DRAM_RULE_1

TAD_DRAM_RULE_2, TAD_DRAM_RULE_3

TAD_DRAM_RULE_4, TAD_DRAM_RULE_5

TAD_DRAM_RULE_6, TAD_DRAM_RULE_7

................................................

58