Intel BX80605I7870 Data Sheet - Page 37

RID - Revision Identification Register, CCR - Class Code Register

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

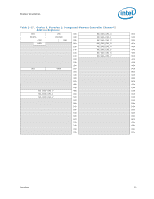

Register Description 2.5.3 2.5.4 RID - Revision Identification Register This register contains the revision number of the processor. The Revision ID (RID) is a traditional 8-bit Read Only (RO) register located at offset 08h in the standard PCI header of every PCI/PCI Express compatible device and function. Device: Function: Offset: 0 0-1 08h Device: Function: Offset: 2 0-1, 4-5 08h Device: Function: Offset: 3 0-2, 4 08h Device: Function: Offset: 4-6 0-3 08h Bit Type Reset Value Description Revision Identification Number 7:0 RO 0h Refer to the Intel® Core™ i7 Processor Extreme Edition and Intel® Core™ i7 Processor Specification Update for the value of the Revision ID Register. CCR - Class Code Register This register contains the Class Code for the device. Writes to this register have no effect. Device: Function: Offset: 0 0-1 09h Device: Function: Offset: 2 0-1, 4-5 09h Device: Function: Offset: 3 0-2, 4 09h Device: Function: Offset: 4-6 0-3 09h Bit 23:16 15:8 7:0 Type RO RO RO Reset Value 06h 0 0 Description Base Class This field indicates the general device category. For the processor, this field is hardwired to 06h, indicating it is a "Bridge Device". Sub-Class This field qualifies the Base Class, providing a more detailed specification of the device function. For all devices the default is 00h, indicating "Host Bridge". Register-Level Programming Interface This field identifies a specific programming interface (if any), that device independent software can use to interact with the device. There are no such interfaces defined for "Host Bridge" types, and this field is hardwired to 00h. Datasheet 37