Intel BX80605I7870 Data Sheet - Page 43

SAD_PAM456

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

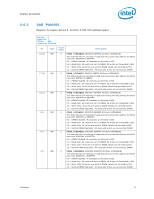

Page 43 highlights

Register Description 2.6.2 SAD_PAM456 Register for legacy device 0, function 0 94h-97h address space. Device: 0 Function: 1 Offset: 44h Access as a Dword Bit 21:20 17:16 13:12 9:8 5:4 1:0 Type RW RW RW RW RW RW Reset Value Description 0 PAM6_HIENABLE. 0EC000h-0EFFFFh Attribute (HIENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0EC000h to 0EFFFFh. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. 0 PAM6_LOENABLE. 0E8000-0EBFFF Attribute (LOENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0E8000 to 0EBFFF. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. 0 PAM5_HIENABLE. 0E4000h-0E7FFFh Attribute (HIENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0E4000h to 0E7FFFh. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. 0 PAM5_LOENABLE. 0E0000h-0E3FFFh Attribute (LOENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0E0000h to 0E3FFFh. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. 0 PAM4_HIENABLE. 0DC000h-0DFFFFh Attribute (HIENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0DC000h to 0DFFFFh. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. 0 PAM4_LOENABLE. 0D8000h-0DBFFFh Attribute (LOENABLE). This field controls the steering of read and write cycles that address the BIOS area from 0D8000h to 0DBFFFh. 00 = DRAM Disabled: All accesses are directed to ESI. 01 = Read Only: All reads are sent to DRAM. All writes are forwarded to ESI. 10 = Write Only: All writes are send to DRAM. Reads are serviced by ESI. 11 = Normal DRAM Operation: All reads and writes are serviced by DRAM. Datasheet 43