Intel BX80605I7870 Data Sheet - Page 34

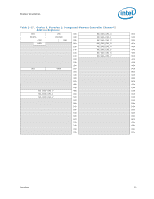

Table 2-18., Device 6, Function 2: Integrated Memory Controller Channel 2, Rank Registers

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 34 highlights

Register Description Table 2-18. Device 6, Function 2: Integrated Memory Controller Channel 2 Rank Registers DID PCISTS CCR HDR VID PCICMD RID SID SVID MC_RIR_LIMIT_CH2_0 MC_RIR_LIMIT_CH2_1 MC_RIR_LIMIT_CH2_2 MC_RIR_LIMIT_CH2_3 MC_RIR_LIMIT_CH2_4 MC_RIR_LIMIT_CH2_5 MC_RIR_LIMIT_CH2_6 MC_RIR_LIMIT_CH2_7 00h 04h 08h 0Ch 10h 14h 18h 1Ch 20h 24h 28h 2Ch 30h 34h 38h 3Ch 40h 44h 48h 4Ch 50h 54h 58h 5Ch 60h 64h 68h 6Ch 70h 74h MC_RIR_WAY_CH2_0 MC_RIR_WAY_CH2_1 MC_RIR_WAY_CH2_2 MC_RIR_WAY_CH2_3 MC_RIR_WAY_CH2_4 MC_RIR_WAY_CH2_5 MC_RIR_WAY_CH2_6 MC_RIR_WAY_CH2_7 MC_RIR_WAY_CH2_8 MC_RIR_WAY_CH2_9 MC_RIR_WAY_CH2_10 MC_RIR_WAY_CH2_11 MC_RIR_WAY_CH2_12 MC_RIR_WAY_CH2_13 MC_RIR_WAY_CH2_14 MC_RIR_WAY_CH2_15 MC_RIR_WAY_CH2_16 MC_RIR_WAY_CH2_17 MC_RIR_WAY_CH2_18 MC_RIR_WAY_CH2_19 MC_RIR_WAY_CH2_20 MC_RIR_WAY_CH2_21 MC_RIR_WAY_CH2_22 MC_RIR_WAY_CH2_23 MC_RIR_WAY_CH2_24 MC_RIR_WAY_CH2_25 MC_RIR_WAY_CH2_26 MC_RIR_WAY_CH2_27 MC_RIR_WAY_CH2_28 MC_RIR_WAY_CH2_29 78h MC_RIR_WAY_CH2_30 7Ch MC_RIR_WAY_CH2_31 80h 84h 88h 8Ch 90h 94h 98h 9Ch A0h A4h A8h ACh B0h B4h B8h BCh C0h C4h C8h CCh D0h D4h D8h DCh E0h E4h E8h ECh F0h F4h F8h FCh 34 Datasheet