Intel BX80605I7870 Data Sheet - Page 80

Mc_tx_bg_cmd_offset_settings_ch0, Mc_tx_bg_cmd_offset_settings_ch1,

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 80 highlights

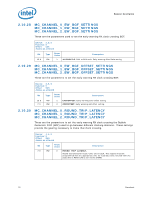

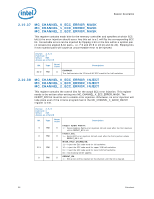

Register Description 2.10.33 MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH0 MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH1 MC_TX_BG_CMD_DATA_RATIO_SETTINGS_CH2 Channel Bubble Generator ratios for CMD and DATA. Device: 4, 5, 6 Function: 0 Offset: E0h Access as a Dword Bit 15:8 7:0 Type RW RW Reset Value Description 1 ALIENRATIO. DCLK to BCLK ratio. 4 NATIVERATIO. UCLK to BCLK ratio. 2.10.34 MC_TX_BG_CMD_OFFSET_SETTINGS_CH0 MC_TX_BG_CMD_OFFSET_SETTINGS_CH1 MC_TX_BG_CMD_OFFSET_SETTINGS_CH2 Integrated Memory Controller Channel Bubble Generator Offsets for CMD FIFO. The Data command FIFOs share the settings for channel 0 across all three channels. The register in Channel 0 must be programmed for all configurations. Device: 4, 5, 6 Function: 0 Offset: E4h Access as a Dword Bit Type Reset Value Description 9:8 RW 7:0 RW 0 PTROFFSET. FIFO pointer offset. 0 BGOFFSET. BG offset. 2.10.35 MC_TX_BG_DATA_OFFSET_SETTINGS_CH0 MC_TX_BG_DATA_OFFSET_SETTINGS_CH1 MC_TX_BG_DATA_OFFSET_SETTINGS_CH2 Integrated Memory Controller Channel Bubble Generator Offsets for DATA FIFO. Device: 4, 5, 6 Function: 0 Offset: E8h Access as a Dword Bit 16:14 13:10 9:8 7:0 Type RW RW RW RW Reset Value Description 0 RDPTROFFSET. Read FIFO pointer offset. 0 WRTPTROFFSET. Write FIFO pointer offset. 0 PTROFFSET. FIFO pointer offset. 0 BGOFFSET. BG offset. 80 Datasheet