Intel BX80605I7870 Data Sheet - Page 58

Tad_interleave_list_4, Tad_interleave_list_5

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 58 highlights

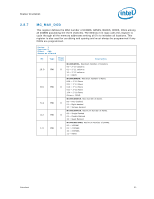

Register Description 2.9.2 TAD_INTERLEAVE_LIST_0, TAD_INTERLEAVE_LIST_1 TAD_INTERLEAVE_LIST_2, TAD_INTERLEAVE_LIST_3 TAD_INTERLEAVE_LIST_4, TAD_INTERLEAVE_LIST_5 TAD_INTERLEAVE_LIST_6, TAD_INTERLEAVE_LIST_7 TAD DRAM package assignments. When the corresponding DRAM_RULE hits, a 3-bit number (determined by mode) is used to index into the Interleave_List Branches to determine which channel the DRAM request belongs to. Device: 3 Function: 1 Offset: C0h, C4h, C8h, CCh, D0h, D4h, D8h, DCh Access as a Dword Bit 29:28 25:24 21:20 17:16 13:12 Type RW RW RW RW RW Reset Value Description Logical Channel7. Index 111 of the Interleave List. Bits determined from the matching TAD_DRAM_RULE mode. - 00 = Logical channel 0 01 = Logical channel 1 10 = Logical channel 2 11 = Reserved Logical Channel6. Index 110 of the Interleave List. Bits determined from the matching TAD_DRAM_RULE mode. - 00 = Logical channel 0 01 = Logical channel 1 10 = Logical channel 2 11 = Reserved Logical Channel5. Index 101 of the Interleave List. Bits determined from the matching TAD_DRAM_RULE mode. - 00 = Logical channel 0 01 = Logical channel 1 10 = Logical channel 2 11 = Reserved Logical Channel4. Index 100 of the Interleave List. Bits determined from the matching TAD_DRAM_RULE mode. - 00 = Logical channel 0 01 = Logical channel 1 10 = Logical channel 2 11 = Reserved Logical Channel3. Index 011 of the Interleave List. Bits determined from the matching TAD_DRAM_RULE mode. - 00 = Logical channel 0 01 = Logical channel 1 10 = Logical channel 2 11 = Reserved 58 Datasheet