Intel BX80605I7870 Data Sheet - Page 56

Mc_scrubaddr_hi

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 56 highlights

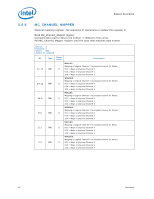

Register Description 2.8.11 MC_SCRUBADDR_HI This register pair contains part of the address of the last patrol scrub request issued. When running memtest, the failing address is logged in this register on memtest errors. Software can write the next address into this register. Scrubbing must be disabled to reliably read and write this register. Device: 3 Function: 0 Offset: 7Ch Access as a Dword Bit Type Reset Value Description 9:8 RW 7:6 RW 5:4 RW 3:0 RW CHNL. 0 This field can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL register. This register is not updated with channel address of the last scrub address issued. DIMM. This field contains the DIMM of the last scrub issued. Can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL register. 0 For writes, to the register this field always contains the Rank ID. For reads, the following translation must be done: If 3 DIMMs are on the channel, then the rank is RANK[0] while the dimm is the concatenation of DIMM[0] and RANK[1]. RANK. This field contains the rank of the last scrub issued. Can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL 0 register.. For writes, to the register this field always contains the rank id. For reads, the following translation must be done: If 3 dimms are on the channel then the rank is RANK[0] while the dimm is the concatenation of DIMM[0] and RANK[1]. BANK. 0 This field contains the bank of the last scrub issued. Can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL register.. 56 Datasheet