Intel BX80605I7870 Data Sheet - Page 55

Mc_crdt_wr_thld, Mc_scrubaddr_lo

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 55 highlights

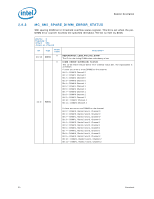

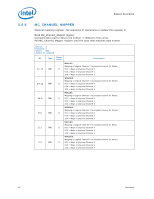

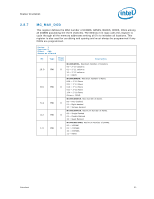

Register Description 2.8.9 2.8.10 MC_CRDT_WR_THLD This is the Memory Controller Write Credit Thresholds register. A Write threshold is defined as the number of credits reserved for this priority (or higher) request. It is required that High threshold be greater than or equal to Crit threshold, and that both be lower than the total Write Credit init value. BIOS must initialize this register with appropriate values depending on the level of Isoch support in the platform. The new values take effect immediately upon being written. Register programming rules: • CRIT threshold value must correspond to the number of critical RTIDs reserved at the IOH. • HIGH threshold value must correspond to the sum of critical and high RTIDs reserved at the IOH (which must not exceed 30). • Set MC_Channel_*_WAQ_PARAMS.ISOCENTRYTHRESHHOLD equal to (31-CRIT). Device: 3 Function: 0 Offset: 74h Access as a Dword Bit 12:8 4:0 Type RW RW Reset Value Description 4 HIGH. High Credit Threshold. 3 CRIT. Critical Credit Threshold. MC_SCRUBADDR_LO This register contains part of the address of the last patrol scrub request issued. When running Memtest, the failing address is logged in this register on Memtest errors. Software can write the next address to be scrubbed into this register. Patrol scrubs must be disabled to reliably write this register. Device: 3 Function: 0 Offset: 78h Access as a Dword Bit 29:14 13:0 Type RW RW Reset Value Description 0 PAGE. This field contains the row of the last scrub issued. Can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL register. 0 COLUMN. This field contains the column of the last scrub issued. Can be written to specify the next scrub address with STARTSCRUB in the MC_SCRUB_CONTROL register. Datasheet 55