Intel BX80605I7870 Data Sheet - Page 87

MC_SAG_CH0_6, MC_SAG_CH0_7, MC_SAG_CH1_0

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 87 highlights

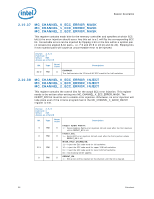

Register Description 2.11.4 Note: MC_SAG_CH0_0, MC_SAG_CH0_1, MC_SAG_CH0_2 MC_SAG_CH0_3, MC_SAG_CH0_4, MC_SAG_CH0_5 MC_SAG_CH0_6, MC_SAG_CH0_7, MC_SAG_CH1_0 MC_SAG_CH1_1, MC_SAG_CH1_2, MC_SAG_CH1_3 MC_SAG_CH1_4, MC_SAG_CH1_5, MC_SAG_CH1_6 MC_SAG_CH1_7, MC_SAG_CH2_0, MC_SAG_CH2_1 MC_SAG_CH2_2, MC_SAG_CH2_3, MC_SAG_CH2_4 MC_SAG_CH2_5, MC_SAG_CH2_6, MC_SAG_CH2_7 Channel Segment Address Registers. For each of the 8 interleave ranges, they specify the offset between the System Address and the Memory Address and the System Address bits used for level 1 interleave, which should not be translated to Memory Address bits. Memory Address is calculated from System Address and the contents of these registers by the following algorithm: m[39:16] = SystemAddress[39:16] + (sign extend {Offset[23:0]}); m[15:6] = SystemAddress[15:6]; If (Removed[2]) {bit 8 removed}; If (Removed[1]) {bit 7 removed}; If (Removed[0]) {bit 6 removed}; MemoryAddress[36:6] = m[36:6]; The following table summarizes the combinations of removed bits and divide-by-3 operations for the various supported interleave configurations. All other combinations are not supported. If any of bits [8:6] are removed, the higher order bits are shifted down. Removed [8:6] 000 001 011 000 001 Divide-By-3 0 0 0 1 1 Interleave None 2-Way 4-Way 3-Way 6-Way Device: 4 Function: 1 Offset: 80h, 84h, 88h, 8Ch, 90h, 94h, 98h, 9Ch Access as a Dword Bit 27 26:24 23:0 Type RW RW RW Reset Value Description DIVBY3. 0 This bit indicates the rule is a 3 or 6 way interleave. REMOVED. 0 These are the bits to be removed after offset subtraction. These bits correspond to System Address [8,7,6]. OFFSET. 0 This value should be subtracted from the current system address to create a contiguous address space within a channel. BITS 9:0 ARE RESERVED AND MUST ALWAYS BE SET TO 0. Datasheet 87