Intel BX80605I7870 Data Sheet - Page 78

Mc_channel_2_ew_bgf_settings

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 78 highlights

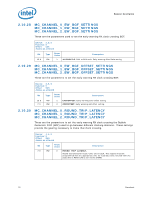

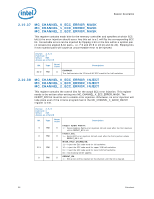

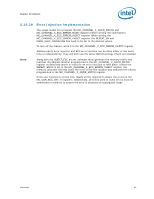

Register Description 2.10.28 MC_CHANNEL_0_EW_BGF_SETTINGS MC_CHANNEL_1_EW_BGF_SETTINGS MC_CHANNEL_2_EW_BGF_SETTINGS These are the parameters used to set the early warning RX clock crossing BGF. Device: 4, 5, 6 Function: 0 Offset: CCh Access as a Dword Bit 15:8 Type RW Reset Value Description 1 ALIENRATIO. Dclk to Bclk ratio. Early warning Alien Ratio setting. 2.10.29 MC_CHANNEL_0_EW_BGF_OFFSET_SETTINGS MC_CHANNEL_1_EW_BGF_OFFSET_SETTINGS MC_CHANNEL_2_EW_BGF_OFFSET_SETTINGS These are the parameters to set the early warning RX clock crossing BGF. Device: 4, 5, 6 Function: 0 Offset: D0h Access as a Dword Bit 15:8 7:0 Type RW RW Reset Value Description 2 EVENOFFSET. Early warning even offset setting. 0 ODDOFFSET. Early warning odd offset setting. 2.10.30 MC_CHANNEL_0_ROUND_TRIP_LATENCY MC_CHANNEL_1_ROUND_TRIP_LATENCY MC_CHANNEL_2_ROUND_TRIP_LATENCY These are the parameters to set the early warning RX clock crossing the Bubble Generator FIFO (BGF) used to go between different clocking domains. These settings provide the gearing necessary to make that clock crossing. Device: 4, 5, 6 Function: 0 Offset: D4h Access as a Dword Bit Type Reset Value Description 7:0 RW 0 ROUND_TRIP_LATENCY. Round trip latency for reads. Units are in UCLK. This register must be programmed with the appropriate time for read data to be retuned from the pads after a READ CAS is sent to the DIMMs. 78 Datasheet