Intel BX80605I7870 Data Sheet - Page 82

Mc_channel_1_ecc_error_mask

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 82 highlights

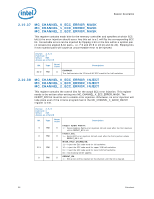

Register Description 2.10.37 MC_CHANNEL_0_ECC_ERROR_MASK MC_CHANNEL_1_ECC_ERROR_MASK MC_CHANNEL_2_ECC_ERROR_MASK This register contains mask bits for the memory controller and specifies at which ECC bit(s) the error injection should occur. Any bits set to a 1 will flip the corresponding ECC bit. Correctable errors can be injected by flipping 1 bit or the bits within a symbol pair (2 consecutive aligned 8-bit pairs - i.e. 7:0 and 15:8 or 23:16 and 31:24). Flipping bits in two symbol pairs will cause an uncorrectable error to be injected. Device: 4, 5, 6 Function: 0 Offset: F8h Access as a Dword Bit 31:0 Type RW Reset Value Description ECCMASK. 0 This field contains the 32 bits of MC ECC mask bit for half cacheline. 2.10.38 MC_CHANNEL_0_ECC_ERROR_INJECT MC_CHANNEL_1_ECC_ERROR_INJECT MC_CHANNEL_2_ECC_ERROR_INJECT This register contains the control bits for the actual ECC error injection. This register needs to be written after writing into MC_CHANNEL_X_ECC_ERROR_MASK. The INJECT_ECC bit must be set to enable error injection. Otherwise, no error injection will take place even if the criteria programmed in the MC_CHANNEL_X_ADDR_MATCH register is met. Device: 4, 5, 6 Function: 0 Offset: FCh Access as a Dword Bit Type Reset Value Description 4 RW 3 RW 2:1 RW 0 RW INJECT_ADDR_PARITY. 0 1 = Forces Address Parity error injection. Bit will reset after the first injection unless REPEAT_EN is set. INJECT_ECC. 0 1 = Forces ECC error injection. Bit will reset after the first injection unless REPEAT_EN is set. MASK_HALF_CACHELINE. 11 = Inject the ECC code word for full cacheline. 0 10 = Inject the ECC code word for upper 32B half cacheline. 01 = Inject the ECC code word for lower 32B half cacheline. 00 = No masking will be applied. 0 REPEAT_EN. 1 = ECC errors will be injected on the channel until the bit is cleared. 82 Datasheet