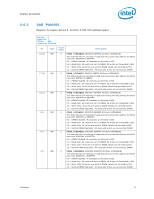

Intel BX80605I7870 Data Sheet - Page 48

Register Description, Channel0_active, Init_done, Divby3en, Channelreset2, Channelreset1,

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 48 highlights

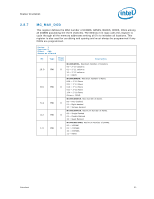

Register Description Device: 3 Function: 0 Offset: 48h Access as a Dword 8 RW 0 7 WO 0 6 RW 0 5 RW 0 4 RW 0 3 RW 0 2 RW 0 1 RW 0 0 RW 0 CHANNEL0_ACTIVE When set, indicate MC channel 0 is active. This bit is controlled (set/reset) by software only. This bit is required to be set for any active channel when INIT_DONE is set by software. Channel 0 AND Channel 1 active must both be set for a lockstep or mirrored pair. INIT_DONE MC initialize complete signal. Setting this bit will exit the training mode of the Integrated Memory Controller and begin normal operation including all enabled maintenance operations. Any CHANNNEL_ACTIVE bits not set when writing a 1 to INIT_DONE will cause the corresponding channel to be disabled. DIVBY3EN Divide By 3 enable. When set, MAD would use the longer pipeline for transactions that are 3 or 6 way interleaved and shorter pipeline for all other transactions. The SAG registers must be appropriately programmed as well. CHANNELRESET2 Reset only the state within the channel. Equivalent to pulling warm reset for that channel. CHANNELRESET1 Reset only the state within the channel. Equivalent to pulling warm reset for that channel. CHANNELRESET0 Reset only the state within the channel. Equivalent to pulling warm reset for that channel. AUTOPRECHARGE. Autoprecharge enable. This bit should be set with the closed page bit. If it is not set with closed page, address decode will be done without setting the autoprecharge bit. ECCEN: ECC Enable ECC Checking enables. When this bit is set in lockstep mode the ECC checking is for the x8 SDDC. ECCEN without Lockstep enables the x4 SDDC ECC checking. CLOSED_PAGE When set, the MC supports a Closed Page policy. The default is Open Page but BIOS should always configure this bit. 48 Datasheet