Intel BX80605I7870 Data Sheet - Page 57

TAD - Target Address Decoder Registers

|

UPC - 735858210461

View all Intel BX80605I7870 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 57 highlights

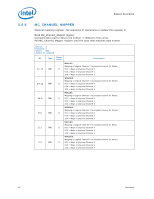

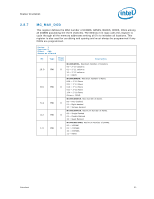

Register Description 2.9 2.9.1 TAD - Target Address Decoder Registers TAD_DRAM_RULE_0, TAD_DRAM_RULE_1 TAD_DRAM_RULE_2, TAD_DRAM_RULE_3 TAD_DRAM_RULE_4, TAD_DRAM_RULE_5 TAD_DRAM_RULE_6, TAD_DRAM_RULE_7 TAD DRAM rules. Address map for channel determination within a package. All addresses sent to this HOME agent must hit a valid enabled DRAM_RULE. No error will be generated if they do not hit a valid location and memory aliasing will happen. Device: 3 Function: 1 Offset: 80h, 84h, 88h, 8Ch, 90h, 94h, 98h, 9Ch Access as a Dword Bit 19:6 2:1 0 Type RW RW RW Reset Value Description LIMIT. - DRAM rule top limit address. Must be strictly greater than previous rule, even if this rule is disabled, unless this rule and all following rules are disabled. Lower limit is the previous rule (or 0 if it is the first rule). MODE. DRAM rule interleave mode. If a DRAM_RULE hits, a 3-bit number is used to index into the corresponding interleave_list to determine which channel the DRAM belongs to. This mode selects how that number is computed. - 00 = Address bits {8,7,6}. 01 = Address bits {8,7,6} XORed with {18,17,16}. 10 = Address bit {6}, MOD3(Address[39..6]). (Note 6 is the high order bit) 11 = Reserved. 0 ENABLE. Enable for DRAM rule. Datasheet 57