HP Superdome SX2000 User Service Guide, Seventh Edition - HP Integrity Superdo - Page 31

Cell Controller, Processor Interface, Cell Board

|

View all HP Superdome SX2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 31 highlights

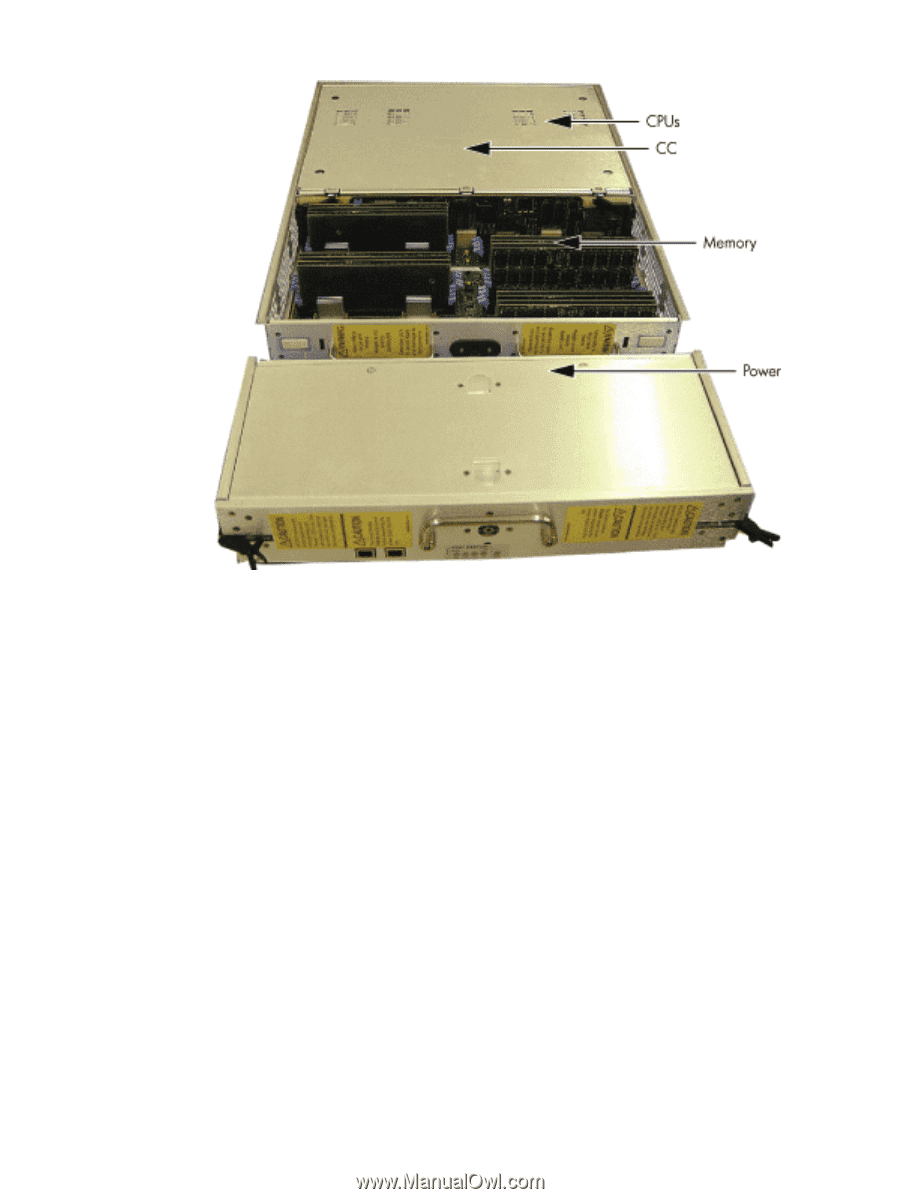

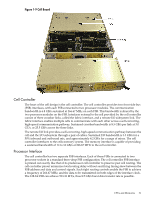

Figure 1-9 Cell Board Cell Controller The heart of the cell design is the cell controller. The cell controller provides two front side bus (FSB) interfaces, with each FSB connected to two processor modules. The communication bandwidth is 6.8 GB/s sustained at 266.67 MHz on each FSB. This bandwidth is shared by the two processor modules on the FSB. Interfaces external to the cell provided by the cell controller consist of three crossbar links, called the fabric interface, and a remote I/O subsystem link. The fabric interface enables multiple cells to communicate with each other across a self-correcting, high-speed communication pathway. Sustained crossbar bandwidth is 8.5 GB/s per link at 3.0 GT/s, or 25.5 GB/s across the three links. The remote I/O link provides a self-correcting, high-speed communication pathway between the cell and the I/O subsystem through a pair of cables. Sustained I/O bandwidth is 5.5 GB/s for a 50% inbound and outbound mix, and approximately 4.2 GB/s for a range of mixes. The cell controller interfaces to the cells memory system. The memory interface is capable of providing a sustained bandwidth of 14 to 16 GB/s at 266.67 MHz to the cell controller. Processor Interface The cell controller has two separate FSB interfaces. Each of those FSBs is connected to two processor sockets in a standard three-drop FSB configuration. The cell controller FSB interface is pinned out exactly like that of its predecessor cell controller to preserve past cell routing. The cell controller pinout minimizes total routing delay without sacrificing timing skew between the FSB address and data and control signals. Such tight routing controls enable the FSB to achieve a frequency of 266.67 MHz, and the data to be transmitted on both edges of the interface clock. The 128-bit FSB can achieve 533.33 MT/s, thus 8.5 GB/s burst data transfer rate is possible. CPUs and Memories 31