HP Superdome SX2000 User Service Guide, Seventh Edition - HP Integrity Superdo - Page 39

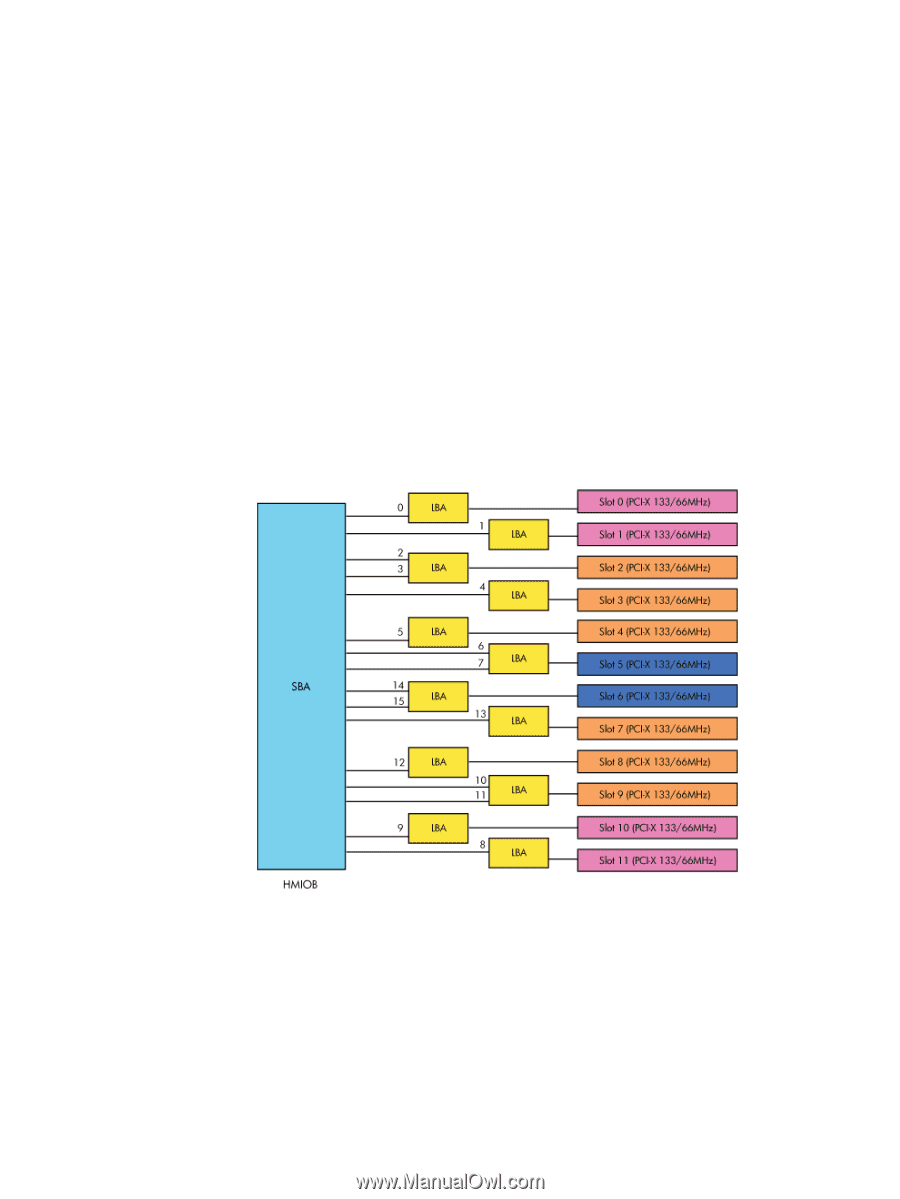

Ropes-to-PCI LBA Chip, PCI-X I/O Rope Mapping

|

View all HP Superdome SX2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

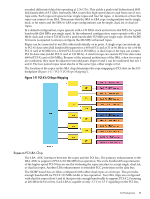

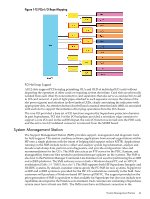

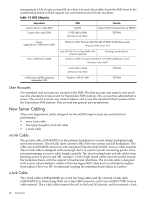

encoded differential data bits operating at 2.36 GT/s. This yields a peak total bidirectional HSS link bandwidth of 8.5 GB/s. Internally, SBA routes this high-speed data to and from one of two rope units. Each rope unit spawns four single ropes and four fat ropes. A maximum of two like ropes can connect to an LBA. This means that the SBA to LBA rope configurations can be single, dual, or fat ropes and the SBA-to-LBA rope configurations can be single, dual, fat or dual fat ropes. In a default configuration, ropes operate with a 133 MHz clock and so have 266 MT/s for a peak bandwidth (266 MB/s per single rope). In the enhanced configuration, ropes operate with a 266 MHz clock and so have 533 MT/s for a peak bandwidth 533 MB/s per single rope. On the SIOBP, firmware is expected to always configure the 266 MHz enhanced ropes. Ropes can be connected to an LBA either individually or in pairs. A single rope can sustain up to PCI 4x data rates (full bandwidth support for a 64-bit PCI card at 33 or 66 MHz or for a 64-bit PCI-X card at 66 MHz for a 32-bit PCI-X card at 133 MHz). A dual rope or fat rope can sustain PCI 8x data rates (64-bit PCI-X card at 133 MHz). A dual fat rope can sustain PCI 16x data rates (64-bit PCI-X card at 266 MHz). Because of the internal architecture of the SBA, when two ropes are combined, they must be adjacent even/odd pairs. Ropes 0 and 1 can be combined, but not 1 and 2. The two paired ropes must also be of the same type, either single or fat. The location of the ropes on the SBA chip determines the rope mapping to PCI slots on the I/O backplane (Figure 1-11 "PCI-X I/O Rope Mapping"). Figure 1-11 PCI-X I/O Rope Mapping Ropes-to-PCI LBA Chip The LBA ASIC interfaces between the ropes and the PCI bus. The primary enhancement to the LBA ASIC is support of PCI-X 2.0 266 MHz bus operation. The extra bandwidth requirements of the higher speed PCI-X bus are met by widening the ropes interface to accept single, dual, fat, or dual fat ropes. Another LBA enhancement is selectable ECC protection on the data bus. The SIOBP board has six LBAs configured with either dual ropes or a fat rope. This provides enough bandwidth for PCI-X 133 MHz 64-bit or less operation. Two LBA chips are configured with dual fat ropes (slots 5 and 6) that provide enough bandwidth to support PCI-X 2.0 running at 266 MHz 64-bit or less. Each LBA is capable of only 3.3 V or 1.5 V signaling on the PCI bus. I/O Subsystem 39