HP Superdome SX2000 User Service Guide, Seventh Edition - HP Integrity Superdo - Page 32

Processors, Cell Memory System, Rules for Processor Mixing

|

View all HP Superdome SX2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 32 highlights

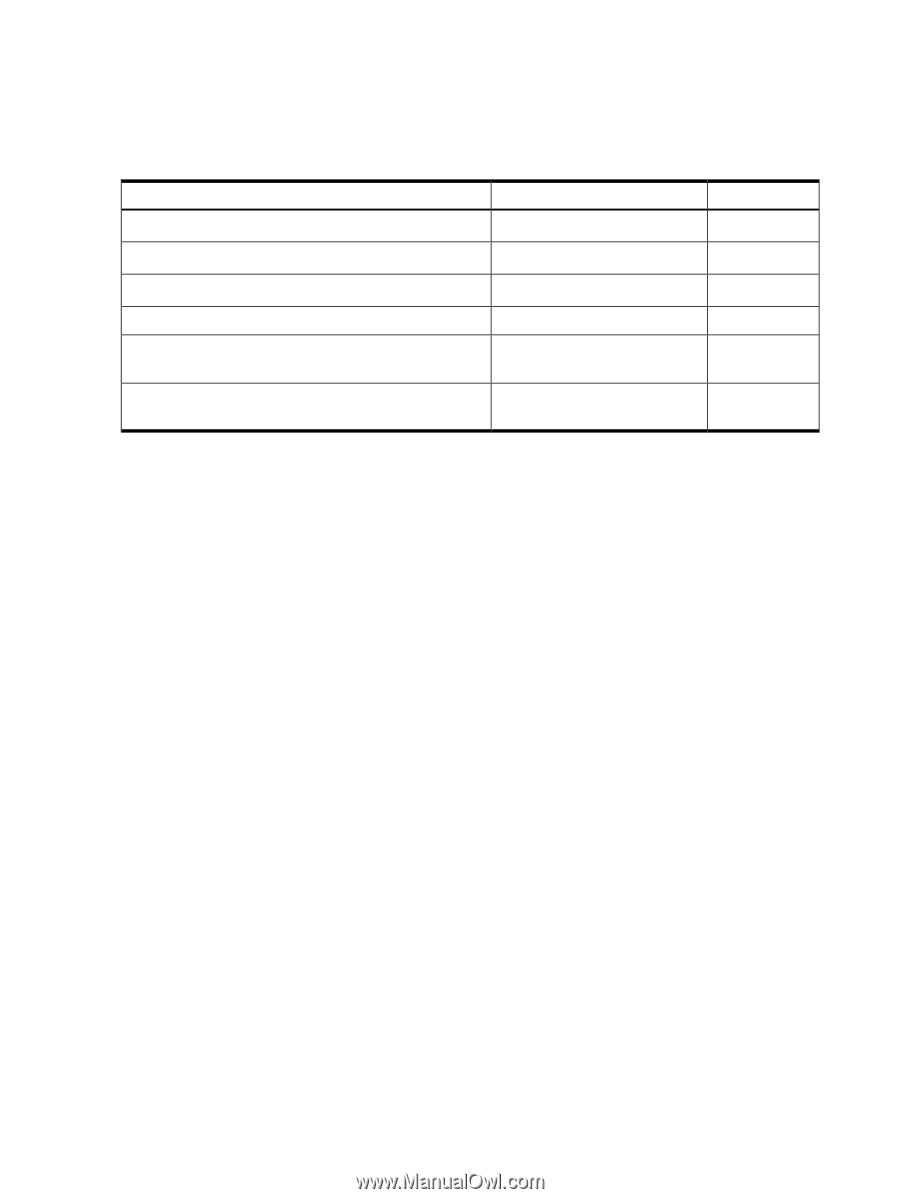

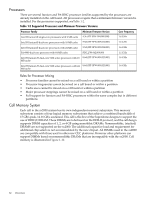

Processors There are several Itanium and PA-RISC processor families supported by the processors are already installed on the cell board. All processors require that a minimum firmware version be installed. For the processors supported, seeTable 1-2. Table 1-2 Supported Processors and Minimum Firmware Versions Processor Family Minimum Firmware Version Intel ® Itanium® single-core processors with 9 MB cache 4.3e (IPF SFW 004.080.000) Intel ® Itanium® dual-core processors with 18 MB cache 5.5d (IPF SFW 005.024.000) Intel ® Itanium® dual-core processors with 24 MB cache 5.5d (IPF SFW 005.024.000) PA-8900 dual-core processor with 64 MB cache PDC_FW 042.009.000 Intel ® Itanium ® dual-core 9100 series processors with 18 8.6d (IPF SFW 009.022.000) MB cache Intel ® Itanium ® dual-core 9100 series processors with 24 8.6d (IPF SFW 009.022.000) MB cache Core Frequency 1.6 GHz 1.6 GHz 1.6 GHz 1.1 GHz 1.6 GHz 1.6 GHz Rules for Processor Mixing • Processor families cannot be mixed on a cell board or within a partition • Processor frequencies cannot be mixed on a cell board or within a partition • Cache sizes cannot be mixed on a cell board or within a partition • Major processor steppings cannot be mixed on a cell board or within a partition • Full support for Itanium and PA-RISC processors within the same complex but in different partitions Cell Memory System Each cell in the sx2000 system has its own independent memory subsystem. This memory subsystem consists of four logical memory subsystems that achieve a combined bandwidth of 17 GB/s peak, 14-16 GB/s sustained. This cell is the first of the Superdome designs to support the use of DDR I/O DRAM. These DIMMs are to be based on the DDR-II protocol, and the cell design supports DIMM capacities of 1, 2, or 4 GB using monolithic DRAMs. Nonmonolithic, (stacked) DRAMS are not supported on the sx2000. The additional capacitive load and requirement for additional chip selects is not accommodated by the new chipset. All DIMMs used in the sx2000 are compatible with those used in other new CEC platforms. However other platforms can support DIMMs based on nonmonolithic DRAMs that are incompatible with the sx2000. Cell memory is illustrated in Figure 1-10. 32 Overview