HP Superdome SX2000 User Service Guide, Seventh Edition - HP Integrity Superdo - Page 40

PCI Slots, Mixed PCI-X and PCI Express I/O Chassis

|

View all HP Superdome SX2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 40 highlights

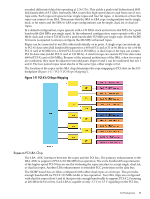

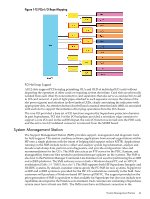

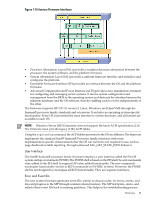

Cards that allow only 5 V signaling are not supported; PCI connector keying prevents insertion of such cards. Each LBA has control and monitor signals for use with a PCI hot-swap chip. It also converts PCI interrupts into interrupt transactions which are fed back to the CPUs. PCI Slots For maximum performance and availability, each PCI slot is sourced by its own LBA chip and is supported by its own portion of a hot-plug controller. All slots are designed to Revision 2.2 of the PCI specification and Revision 2.0a of the PCI-X specification and can support full size 64-bit cards with the exceptions noted below. Shorter or smaller cards are also supported, as are 32-bit cards. Slot 0 support for the core I/O card is removed on the SIOBP. SIOBP PCI slot support of VAUX3.3 and PME is not be supported. SMBus is supported in hardware through two I2C Muxes. Firmware can configure the muxes to enable communication to any of the 12 PCI slots. JTAG is not supported for PCI slots. Each device on a PCI bus is assigned a physical device number. On the past HIOB, the slot was configured as device 0. However, the PCI-X specification requires that the host bridge to be device 0. So for SIOBP the slot is configured as device 1. The SIOBP's ten outermost slots support only 3.3 V signaling (PCI or PCI-X Mode 1). The two innermost slots support either 3.3 V or 1.5 V (PCI-X Mode 2) signaling. All SIOBP PCI connectors physically prevent 5 V signaling cards from being installed. Mixed PCI-X and PCI Express I/O Chassis The 12-slot mixed PCI-X/PCI Express (PCIe) I/O chassis was introduced for the sx2000 Superdome with the two new dual-core Intel ® Itanium® processors and is heavily leveraged from the 12-slot PCI-X I/O chassis. The primary change replaces six of the LBAs with a new LBA ASIC to provide six PCI Express 1.1 compliant slots. The PCI-X/PCIe I/O chassis is only supported for Intel ® Itanium® dual-core processors. The new LBA provides an 8-lane (x8) Root Port compliant with the PCIe 1.1 specification. The six corresponding slots are compatible with PCIe cards with x8 or smaller edge connectors. PCIe slots are not compatible with PCI or PCI-X cards. Physical keying prevents installation of PCI or PCI-X cards into PCIe slots, or PCIe cards into PCI-X slots. The new PCIe I/O backplane board is a respin of the SIOBP3, with six of the LBA ASICs replaced with new PCIe LBA ASICs. These new LBA ASICs populate slots 2, 3, 4, 5, 6, and 7. All other slots contain PCI LBA ASICs. Slot 2 is a dual-thin rope; slots 3, 4, and 7 are fat-ropes and slots 5 and 6 are dual-fat ropes. All slots are hot-pluggable (Figure 1-12 "PCIe I/O Rope Mapping"). The new AIOBP I/O backplane uses most of the same mechanical components as the SIOBP. The differences are the PCIe connector, and the card extractor hardware. A PCI-X I/O chassis consists of four printed circuit assemblies; the PCI-X I/O backplane, the PCI-X I/O power board, the PCI-X I/O power transfer board, and the doorbell board plus the necessary mechanical components required to support 12 PCI card slots. 40 Overview